【導(dǎo)讀】當(dāng)你在選擇電容時,面對形形色色的該如何選擇呢?筆者分別來談一談常見的一些電容和其普遍的適用范圍。注意:電容種類實(shí)在太多,所以這里只會涉及微電子電路設(shè)計(jì)中常見電容的使用的。譬如那些什么可變電容,超級電容等等暫時先不會覆蓋到。

筆者分別來談一談常見的一些電容和其普遍的適用范圍。注意:電容種類實(shí)在太多,所以這里只會涉及微電子電路設(shè)計(jì)中常見電容的使用的。

當(dāng)你在選擇電容時,面對形形色色的該如何選擇呢?筆者分別來談一談常見的一些電容和其普遍的適用范圍。注意:電容種類實(shí)在太多,所以這里只會涉及微電子電路設(shè)計(jì)中常見電容的使用的。譬如那些什么可變電容,超級電容等等暫時先不會覆蓋到。

Ceramic Capacitor(陶瓷電容-無極性電容):

Pros:低ESR,很好的高頻特性,穩(wěn)定性高,溫度系數(shù)小。Cons:電容值相對較低(幾pF to 幾十uF),脆弱易受損,電容值受電壓影響較大

陶瓷電容幾乎是目前使用最最多的一種電容,常見用于去耦,信號耦合和模擬濾波器設(shè)計(jì)等等?,F(xiàn)在工藝越來越好,大容值的陶瓷電容也能買到,只不過價錢相對較高?,F(xiàn)在通常PCB的密度很高尺寸小,尤其是消費(fèi)電子,很少會再見到使用leaded cap,常用的封裝目前來說幾乎都是貼片的。由于制作工藝的限制,低ESR電容的容值一般不會太高。

Electrolytic capacitor(電解電容-有極性電容):

Pros:高容值,相對便宜,不易受損,電容值受電壓影響小。Cons:高ESR,ESL,很差的高頻特性,穩(wěn)定性低,溫度系數(shù)高

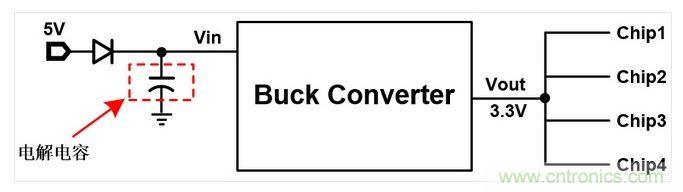

電解電容在電源電路里是很常見的,通常電容值比較大,從幾個uF到幾千uF的容值你都可以找的到。因?yàn)槠涓呷葜担哳l特性差的特點(diǎn)(通常< 100kHz),常被用作輸入電源的去耦穩(wěn)壓。要注意的是這里的電源不是指的芯片的Vdd或者Vcc,我所指的是比如你 PCB 的power總電源模塊,例如一個5V的DC輸入到一個Buck converter轉(zhuǎn)成3.3V的DC給你PCB上其他各種芯片供電,通常電解電容是被接在這個5V電源和ground之間的。

上圖是我簡單畫的一個常用的電源模塊設(shè)計(jì),假如5V是整個PCB的總電源,一般這個電源后面放的去耦電容會使用電解電容,因?yàn)樵谶@個位置我們通常不會太過多關(guān)注高頻去耦,所以可以用相對較低的價錢得到一個較大的電容來去耦穩(wěn)壓。講到這里,可能有人會問,我可以用陶瓷電容來替代這個電解電容嗎?可以,也不可以。再解釋這個之前,我們先來講一下兩種電容的容值v.s.電壓的關(guān)系??聪聢D

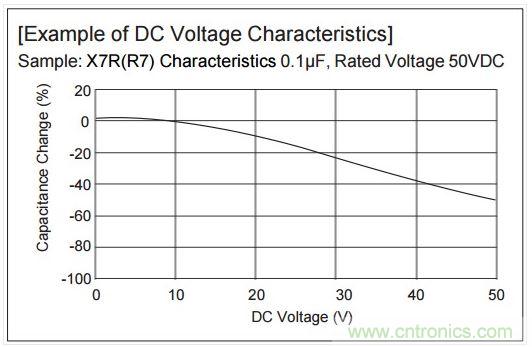

這是我隨便從Murata的一個陶瓷電容的datasheet上面截的一個電容變化v.s.電壓的plot。很明顯的可以看出來電容的值對于對其所加的電壓不是一個恒定的值,也就是說對于上面這個電容,10V的時候電容值是0.1uF而電壓變?yōu)?0V時其實(shí)只有0.05uF。而電解電容的有點(diǎn)就在于它比陶瓷電容有更小的voltage dependency。其實(shí)電容值不僅僅會跟隨電壓變化而變化,還會根據(jù)溫度的變化而變化,在這一點(diǎn)上電解電容是不如陶瓷電容的。從DFM(Design for manufacturability)和reliability的角度來說,電解電容一般都比較大,對于集成度超高的PCB很難fit進(jìn)去。電解電容比陶瓷電容對物理損壞的抗性要高得多,尤其是在flex pcb上,陶瓷電容很容易受切損。但是在reliability上講,陶瓷電容卻又比電解電容要好。

電解電容其實(shí)是一個大類,常見的是鋁電解電容。還有鉭電解電容等等。比如鉭電容,它改善了鋁電解電容的一些缺點(diǎn),其容值密度更高,有更好的高頻特性,更reliable。但是!鉭電容對于反向電壓的容忍性極差,如果電壓反向了或所加電壓高于額定電壓會很容易"爆"。

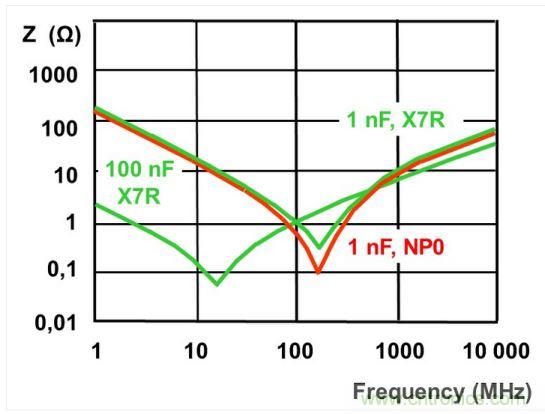

Decoupling Cap and PCB Layout

電容的頻響特征,決定其頻響特征的是ESR,ESL,和本身的C。在日常設(shè)計(jì)中,對layout比較critical的電容通常是去耦電容。常見的去耦電容使用都是一個大的+一個小的,因?yàn)槿葜敌〉碾娙萜毡橛懈〉腅SR,ESL,意味著在高頻它整體看上去仍然會像一個電容而不是電感。這樣的話就可以彌補(bǔ)大電容所覆蓋不到的高頻。正如下圖所示,把一個100nF和一個1nF的阻抗頻率特征曲線放在一起整體容性可以覆蓋到將近200MHz,而單單100nF只能大概到20MHz。

所以最基本的PCB layout rule,把去耦電容放的離你芯片的pin越近越好,因?yàn)橐WCPCB trace的寄生電阻,電感最小,這不僅僅是從Power到電容,還包括電容到ground!其次,放置電容時要遠(yuǎn)離噪聲高的或者高頻數(shù)字信號的線路。

對于微電子設(shè)計(jì),可以說這兩類電容幾乎覆蓋了平時所用到電容的90%以上。(其實(shí)我目前為止也很少接觸其他種類電容)。當(dāng)然了,如果你有興趣了解其他電容,網(wǎng)上有很多信息可以去看,無非就是性能上的差別。關(guān)鍵在于設(shè)計(jì)時要把之前所提到不同電容的優(yōu)點(diǎn)和缺點(diǎn)考慮進(jìn)去,想想這些優(yōu)缺點(diǎn)加進(jìn)去會對你的電路造成什么樣的影響?影響具體是多少?想明白了你才能做出正確的決定,從而選到一個最合適的電容。

留幾個我面試時關(guān)于電容常問的問題

1、為什么容值較大的陶瓷電容在加上電壓工作時會發(fā)出聲音?比如DC-DC converter的output capacitor。

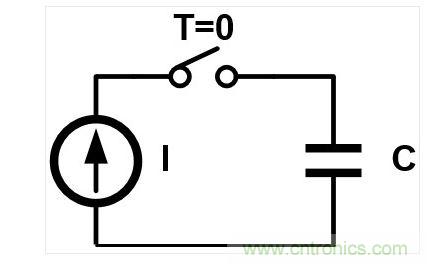

2、如下圖所示,電容C是一個常見的陶瓷電容(非理想器件),容值為C=100nF,ESR=30mΩ,ESL=1nH,Rated Voltage為5V。電流源I為理想電流源。[Hints:請考慮一切可能發(fā)生的事情]

在T=0時開關(guān)關(guān)閉,請解釋從T=0開始電容兩端電壓的變化,容值的變化。畫出經(jīng)過電容C的電流和兩端的電壓相對于時間的曲線。 如果下圖理想電流源換成理想電壓源V=3V,請問電容充電到99%需要多長時間?

還是使用理想電壓源對這個電容C充電充到電壓V1。根據(jù)公式,儲存在電容上的總能量為E=½CV²,而C=Q/V,所以E=½QV。但是理想電壓源輸出的總能量P=QV。為什么充電后到達(dá)電容C的能量只有一半?

再進(jìn)階一點(diǎn)問題,有什么方法可以將充電的能量損失降低到接近零?