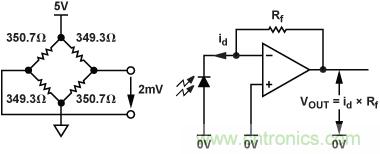

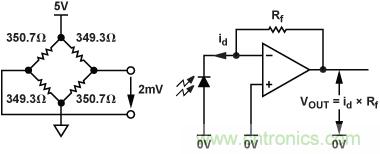

【導(dǎo)讀】電子行業(yè)經(jīng)常需要測量寬動(dòng)態(tài)范圍信號(hào)�����,但目前的技術(shù)常常難以滿足系統(tǒng)的實(shí)際要求�����。電子秤系統(tǒng)通常采用稱重橋式傳感器�,最大滿量程輸出為1 mV至2 mV。這種系統(tǒng)要求分辨率約為1000000:1,折合到2 mV輸入端時(shí)��,需要高性能�、低噪聲、高增益放大器和∑-?調(diào)制器。與此類似�����,醫(yī)療應(yīng)用中進(jìn)行化學(xué)和血液分析時(shí)經(jīng)常會(huì)采用光電二極管傳感器�,產(chǎn)生的電流很小,需要精確測量(如圖1所示)�����。通常采用的是低噪聲跨導(dǎo)放大器���,該放大器有多級(jí)增益和后處理功能。

圖1. 稱重傳感器和光電二極管應(yīng)用的輸入

盡管實(shí)際傳感器數(shù)據(jù)通常只占輸入信號(hào)范圍的一小部分�����,但系統(tǒng)往往必須經(jīng)過專門設(shè)計(jì)以處理故障情況���。因此,寬動(dòng)態(tài)范圍��、高性能(且輸入較?���。┮约皩?duì)快速變化信號(hào)的迅速響應(yīng)就成了關(guān)鍵要求���。有些應(yīng)用(如振動(dòng)監(jiān)控系統(tǒng))包含交流和直流兩種信息,因此���,具備精確監(jiān)控大小兩種信號(hào)的能力變得越來越重要����。

要滿足這些要求���,需要有靈活的信號(hào)調(diào)理模塊���、低噪聲輸入�、較高的增益�����,還要能夠在不影響性能的前提下動(dòng)態(tài)改變?cè)鲆嬉皂憫?yīng)輸入電平變化��,同時(shí)依然維持寬動(dòng)態(tài)范圍?�,F(xiàn)有的∑-? 技術(shù)能夠提供很多應(yīng)用所需的動(dòng)態(tài)范圍����,但要犧牲更新速率。本文提出了一種替代方法�����,即結(jié)合采用高速逐次逼近型采樣ADC和自動(dòng)調(diào)節(jié)量程的可編程增益放大器(PGA)前端。鑒于增益會(huì)根據(jù)模擬輸入值自動(dòng)改變��,這種方法采用過采樣將系統(tǒng)的動(dòng)態(tài)范圍增加至126 dB以上����。

技術(shù)

在ADC應(yīng)用中����,動(dòng)態(tài)范圍是指滿量程均方根值與均方根噪聲之比���,通常將模擬輸入短接在一起測得�����。動(dòng)態(tài)范圍通常以分貝表示 (dBV = 20 × log10 電壓比)表示ADC能夠辨識(shí)的信號(hào)幅度范圍;動(dòng)態(tài)范圍為60 dB的ADC可辨識(shí)的信號(hào)幅度范圍為1000:1。N位ADC的動(dòng)態(tài)范圍(DR)計(jì)算公式如下:

DR = 6.021N + 1.763 dB

∑-? ADC,(如AD7767, 可以通過結(jié)合∑-? 調(diào)制器和數(shù)字后置處理器實(shí)現(xiàn)出色的動(dòng)態(tài)范圍����。轉(zhuǎn)換器之后的數(shù)字濾波用于消除帶外量化噪聲,它還可以將數(shù)據(jù)速率從濾波器輸入端的fMCLK, 降低到數(shù)字輸出端的fMCLK/8, fMCLK/16, 或fMCLK/32, 具體取決于所用器件的型號(hào)。要提高動(dòng)態(tài)范圍,可以添加低噪聲PGA��,通過調(diào)理輸入信號(hào)來實(shí)現(xiàn)滿量程�����。系統(tǒng)的本底噪聲主要表現(xiàn)為前端PGA的輸入噪聲���,后者取決于增益設(shè)置。如果信號(hào)太大,就會(huì)超出ADC輸入的量程。如果信號(hào)太小�����,就會(huì)在轉(zhuǎn)換器的量化噪聲中丟失。∑-? ADC往往用于需要較低系統(tǒng)更新速率的應(yīng)用����。

對(duì)逐次逼近型ADC進(jìn)行過采樣以提高動(dòng)態(tài)范圍

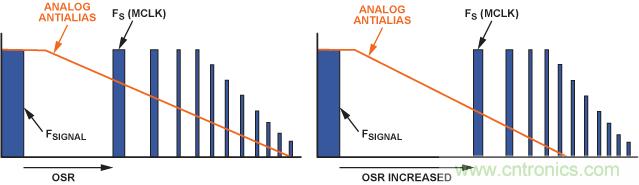

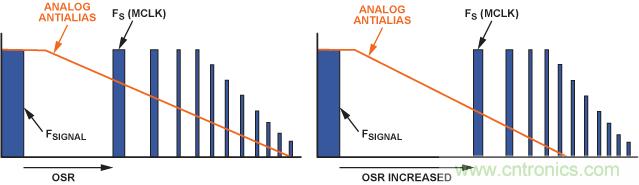

提高逐次逼近型ADC動(dòng)態(tài)范圍的方法之一是實(shí)施過采樣�����,即以遠(yuǎn)高于奈奎斯特頻率的速率完成輸入信號(hào)的采樣過程��。一般說來����,采樣頻率每增加一倍�����,噪聲性能就會(huì)提升約3 dB(如圖2所示)�����。過采樣可通過后處理技術(shù)以數(shù)字形式完成����。有些ADC (如 AD7606, 具有可編程過采樣率,最終用戶可以選擇合適的過采樣率�。

圖2. 通過過采樣減少噪聲

PGA功能與過采樣相結(jié)合

要實(shí)現(xiàn)最大動(dòng)態(tài)范圍,可以添加前端PGA級(jí)���,從而提高極小信號(hào)輸入的有效信噪比(SNR)�����。假設(shè)系統(tǒng)動(dòng)態(tài)范圍要求為126 dB以上���,首先,計(jì)算出最小均方根噪聲��,以實(shí)現(xiàn)該動(dòng)態(tài)范圍�����。例如�,3 V的輸入范圍(6 V p-p)具有2.12 V的滿量程均方根值(6/2√2)。最大系統(tǒng)容許噪聲計(jì)算公式如下:

126 dB = 20 log (2.12 V/rms noise)

因此 rms 噪聲≈ 1 µV rms.

現(xiàn)在�����,考慮系統(tǒng)更新速率�����,系統(tǒng)更新速率決定了過采樣速率和系統(tǒng)所能容許的最大噪聲量(折合到輸入端(RTI))���。例如AD7985 16-bit, 2.5-MSPS PulSAR®是一款16位�����、2.5 MSPS PulSAR® ADC���,當(dāng)該器件運(yùn)行于600 kSPS(功耗11 mW),過采樣率為72時(shí)�,輸入信號(hào)限制在大約4 kHz帶寬內(nèi)。噪聲密度(ND)乘以√f即可得出總均方根噪聲�����,因此�,最大容許輸入頻譜噪聲密度(ND)計(jì)算公式如下:

1 μV rms = ND × √4 kHz

或, ND = 15.5 nV/√Hz

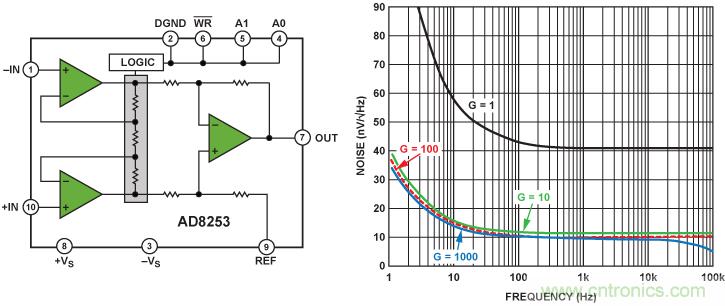

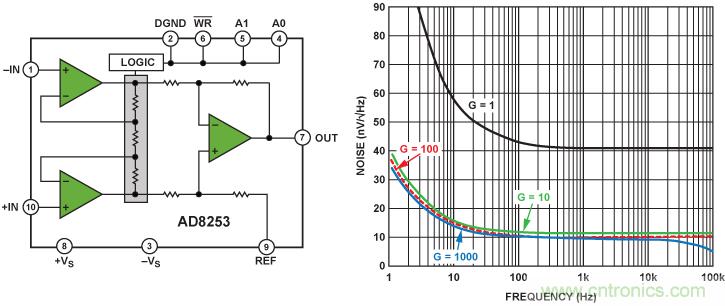

從RTI系統(tǒng)輸入噪聲的這一品質(zhì)因數(shù)來看,可以選擇適當(dāng)?shù)膬x表放大器來提供足夠的模擬前端增益(與ADC的信噪比相加并具有相關(guān)過采樣時(shí))��,從而實(shí)現(xiàn)所需的126 dB��。AD7985的典型信噪比值為89 dB���,72倍過采樣會(huì)進(jìn)一步將信噪比增加約18 dB(72 接近26�,相當(dāng)于每倍增一次增加3 dB)���。要實(shí)現(xiàn)126 dB的動(dòng)態(tài)范圍�����,還需要再增加20 dB���,這可以通過模擬PGA級(jí)的增益來提供。儀表放大器必須提供≥20的增益(或至少不能超過15.5 nV/√Hz的噪聲密度指標(biāo))����。AD8253是很好的選擇,它是一款10 MHz��、20 V/µs����、G = 1�、10�����、100的1000iCMOS®可編程增益儀表放大器���,具有低噪聲����、10 nV/√Hz輸入級(jí)�,增益為100,滿足所需帶寬��,如圖3所示�����。

圖3. AD8253儀表放大器:框圖和噪聲頻譜密度

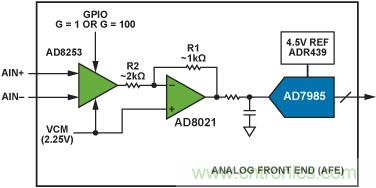

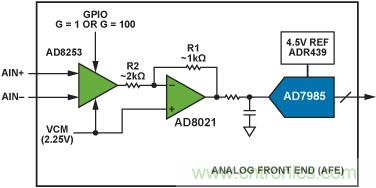

圖4所示為采用前端PGA增益和ADC過采樣的系統(tǒng)級(jí)解決方案�。AD8021是一款2.1 nV/√Hz的低噪聲高速放大器,能夠驅(qū)動(dòng)AD7985����,還可以偏置或衰減AD8253的輸出。AD8253和AD8021都采用外部共模偏置電壓工作�,可共同確保ADC的輸入具有相同的共模電壓���。

圖4. 低噪聲寬帶模擬前端.

由于整個(gè)系統(tǒng)的噪聲預(yù)算為最大15 nV/√Hz折合到輸入端 (RTI),必要計(jì)算每個(gè)模塊的主要噪聲源�����,確保不會(huì)超過15 nV/√Hz的強(qiáng)制限幅。AD8021折合到輸入端的噪聲值小于3 nV/√Hz��,當(dāng)折合到增益為100的AD8253級(jí)的輸入端時(shí)可忽略不計(jì)。AD7985的額定信噪比為89 dB����,采用外部4.5 V基準(zhǔn)電壓源��,適用的噪聲分辨率小于45 μV rms���。假設(shè)ADC的奈奎斯特帶寬為300 kHz�,在該帶寬范圍內(nèi)會(huì)產(chǎn)生約83 nV/√Hz的噪聲����。折合到AD7985輸入端時(shí)���,其小于1 nV/√Hz的噪聲在系統(tǒng)中可忽略不計(jì),因?yàn)槠渲械腞TI噪聲源是用平方和的平方根計(jì)算方法相加的�����。

采用AD8253的另一個(gè)好處是具有數(shù)字增益控制��,可使系統(tǒng)增益進(jìn)行動(dòng)態(tài)變化以響應(yīng)輸入變化。這一功能可通過系統(tǒng)的數(shù)字信號(hào)處理能力智能化實(shí)現(xiàn)���。

在該應(yīng)用中��,數(shù)字處理的主要功能是利用AD7985 16位轉(zhuǎn)換結(jié)果產(chǎn)生高分辨率輸出���。該功能通過自動(dòng)抽取數(shù)據(jù)和切換模擬輸入增益實(shí)現(xiàn)(具體取決于輸入幅度)。這種過采樣產(chǎn)生的輸出數(shù)據(jù)速率低于ADC采樣速率����,但是動(dòng)態(tài)范圍大大增加。

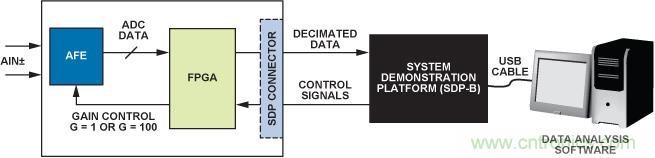

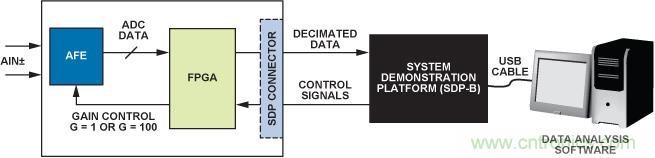

要對(duì)該應(yīng)用的數(shù)字端進(jìn)行原型設(shè)計(jì)����,應(yīng)采用現(xiàn)場可編程門陣列(FPGA)作為數(shù)字內(nèi)核���。為了快速調(diào)試系統(tǒng)�����,模擬電路和FPGA整合到了一塊電路板上�����,如圖5所示�����,采用了 系統(tǒng)演示平臺(tái) (SDP) 連接器標(biāo)準(zhǔn),可以輕松通過USB連接到PC�����。SDP結(jié)合了可重復(fù)使用的硬件和軟件���,可以通過最常用的器件接口輕松控制硬件并從中捕捉數(shù)據(jù)���。

圖5. 在包含F(xiàn)PGA�����、SDP和PC的系統(tǒng)中采用模擬前端(AFE)

基本控制流如下:

● 先上電���,然后校零。將AD8253的差分模擬輸入端對(duì)地短接,每次增益設(shè)置時(shí)進(jìn)行AD7985轉(zhuǎn)換�。存儲(chǔ)ADC值,以供稍后使用�����。

● 校準(zhǔn)完成后��,F(xiàn)PGA以預(yù)設(shè)速率向AD7985發(fā)出一個(gè)周期轉(zhuǎn)換開始信號(hào)����,本例中約為600 kSPS。每個(gè)ADC結(jié)果都讀入FPGA��,并同時(shí)傳遞至抽取和增益模塊��。

● 增益模塊檢查當(dāng)前的ADC結(jié)果�����、之前的ADC結(jié)果和當(dāng)前的增益設(shè)置����,然后確定對(duì)下一次ADC轉(zhuǎn)換最合適的增益設(shè)置�。下面將詳細(xì)介紹這一過程���。

● 抽取模塊處理每個(gè)ADC樣本及其當(dāng)前PGA增益設(shè)置����,以及之前存儲(chǔ)的校準(zhǔn)值�。收到72個(gè)ADC樣本后,23位輸出結(jié)果就是72個(gè)樣本的平均值����,其中考慮了失調(diào)和增益��。

● 然后���,該23位結(jié)果會(huì)轉(zhuǎn)換成二進(jìn)制補(bǔ)碼,以兼容Blackfin串口(SPORT)的格式從FPGA接收�,并由SDP-B硬件捕捉。該過程每隔72個(gè)樣本采用新數(shù)據(jù)字重復(fù)進(jìn)行�����。

FPGA中采用的兩個(gè)主要模塊是抽取器和增益計(jì)算器。下面將詳細(xì)介紹每個(gè)模塊���。

抽取器

該模塊具有內(nèi)部狀態(tài)機(jī),可以管理一些連續(xù)的數(shù)據(jù)處理步驟:

每個(gè)AD7985樣本都?xì)w一化為相同的比例�。例如:AD7985輸入4 mV����,基準(zhǔn)電壓4.5 V���,得出代碼(4 mV/4.5 V × 65535) = 58���,G = 1��。G = 100時(shí)��,ADC輸入端獲得電壓為400 mV�,得出輸出代碼為5825。對(duì)模擬前端增益(AFE)為1的ADC樣本而言,當(dāng)AFE增益為100時(shí)�����,樣本必須乘以100�����,以抵消比例影響。這樣就能保證這些樣本能夠正確求得平均值且合理抽取����,而不受AFE增益設(shè)置的影響。

抽取器功能就位后���,就可以對(duì)模擬輸入進(jìn)行初始測試�。

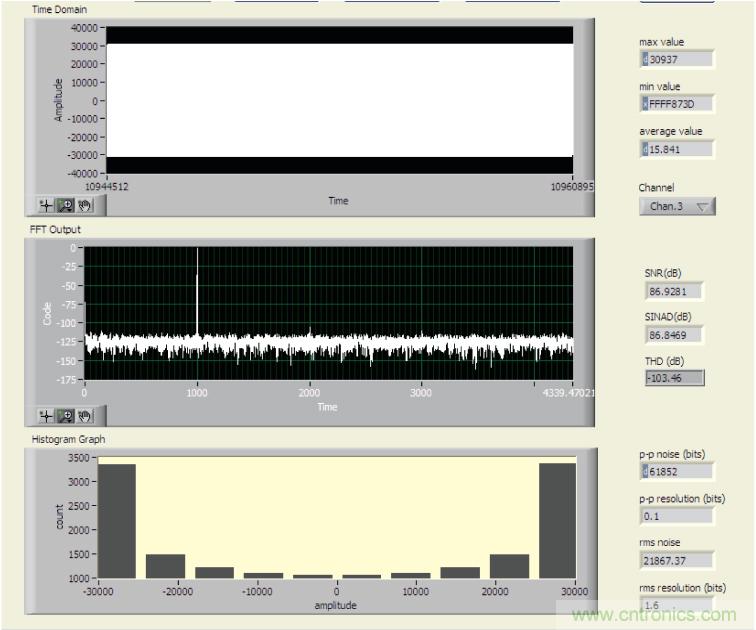

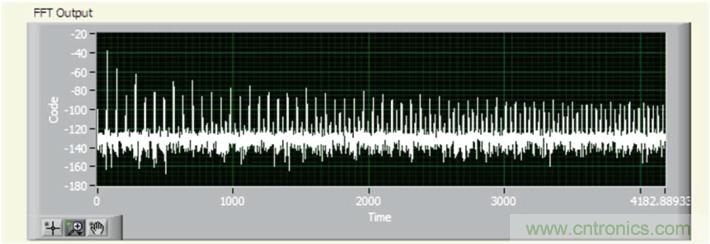

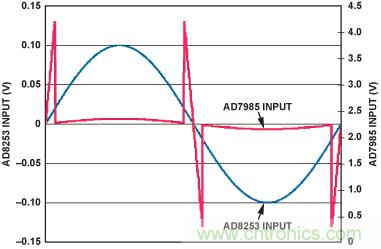

將輸入短接����,系統(tǒng)就能在高增益直流模式下測試(如圖6所示)�����。

圖6. 輸入短接時(shí)的系統(tǒng)高增益直流模式噪聲測試

結(jié)果顯示,p-p噪聲為6位�,均方根噪聲出色,為0.654 µV rms(0.84 LSB��,16位)�����。2.12 V均方根滿量程范圍時(shí)����,動(dòng)態(tài)范圍計(jì)算公式如下:

DR = 20 log10(FS/rms noise) = ~130 dB

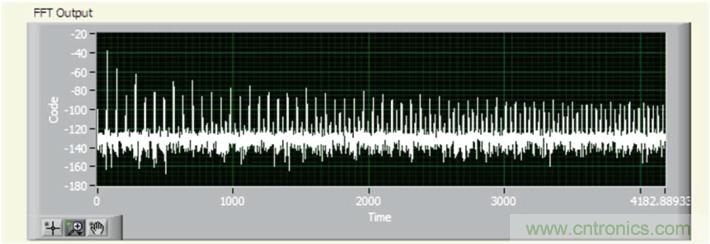

因此�,系統(tǒng)很容易滿足有關(guān)噪聲的動(dòng)態(tài)范圍目標(biāo)��。采用50 mV p-p交流模擬輸入進(jìn)行測試時(shí)��,頻域出現(xiàn)重大失真(如圖7所示)���。這一特定輸入幅度突出表明了系統(tǒng)的最差情況——即交流輸入幅度略大于增益 為100的模式所處理的范圍�����,而且系統(tǒng)經(jīng)常在兩種模式之間切換�����。選擇增益閾值也會(huì)加重這一范圍切換效應(yīng)問題�����,詳見下文所述���。每個(gè)增益模式失調(diào)之間的不匹配會(huì)以總諧波失真形式顯示出來,因?yàn)橛?jì)算出的輸出碼的跳變幅度為每個(gè)范圍中各失調(diào)之差�����。

圖7. 無校準(zhǔn)時(shí)的最差情況輸入幅度

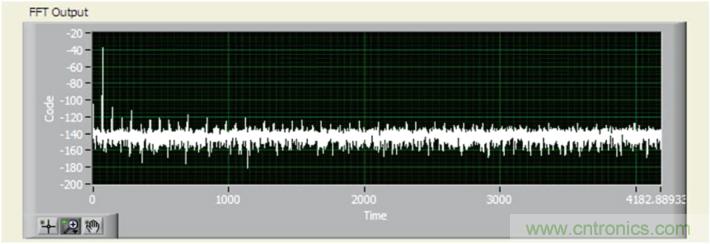

只要通過校準(zhǔn)消除每個(gè)增益范圍的零失調(diào),就會(huì)明顯減少信號(hào)失真���。實(shí)際上���,單憑校準(zhǔn)就可以減少約50 dB的諧波����,如圖8所示。即使輸入音處于最差情況�����,諧波也可以減少至–110 dB滿量程水平����。

圖8. 無校準(zhǔn)時(shí)的最差情況輸入幅度

校準(zhǔn)后的失調(diào)從歸一化的樣本中去除。由于兩種增益設(shè)置時(shí)都進(jìn)行了校準(zhǔn)����,去除的失調(diào)取決于ADC采樣時(shí)的增益。

經(jīng)過歸一化和失調(diào)校準(zhǔn)后的樣本添加至累加器寄存器�����,累加器寄存器上電時(shí)可復(fù)位,每次接收72個(gè)樣本��。72個(gè)樣本接收完成且添加至累加器后�,總和傳遞至除法器,除法器將累加器中的值除以72�,產(chǎn)生一個(gè)23位的平均值。此時(shí)會(huì)設(shè)置輸出標(biāo)志��,說明除法完成����,新的結(jié)果已就緒。

增益設(shè)置

該模塊根據(jù)當(dāng)前的增益設(shè)置��、兩個(gè)原始ADC樣本和一些硬編碼閾值來輸出新的增益設(shè)置��。系統(tǒng)采用四個(gè)閾值�;這些閾值的選擇對(duì)最大限度地增加系統(tǒng)的模擬輸入范圍至關(guān)重要,保證G = 100模式用于盡可能多的信號(hào)范圍�����,同時(shí)防止超過ADC輸入的量程�。注意�,該增益模塊的運(yùn)行基于每個(gè)原始ADC結(jié)果��,而非經(jīng)過歸一化的數(shù)據(jù)���。記住這一點(diǎn)后���,下面將舉例說明可用于此類系統(tǒng)的一些閾值(假設(shè)為雙極性系統(tǒng),中量程為0):

T1(正下閾值):+162(高于中量程162個(gè)代碼)

T2(負(fù)下閾值):-162(低于中量程162個(gè)代碼)

T3(正上閾值):+32507(低于正滿量程260個(gè)代碼)

T4(負(fù)上閾值):–32508(高于負(fù)滿量程260個(gè)代碼)

處于G = 1模式時(shí)���,采用內(nèi)限值T1和T2。當(dāng)實(shí)際ADC結(jié)果處于T1和T2之間時(shí)��,增益切換至G = 100模式����。這樣可以確保ADC接收到的模擬輸入電壓盡快最大化。

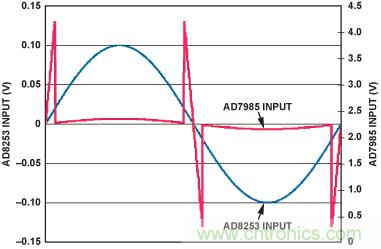

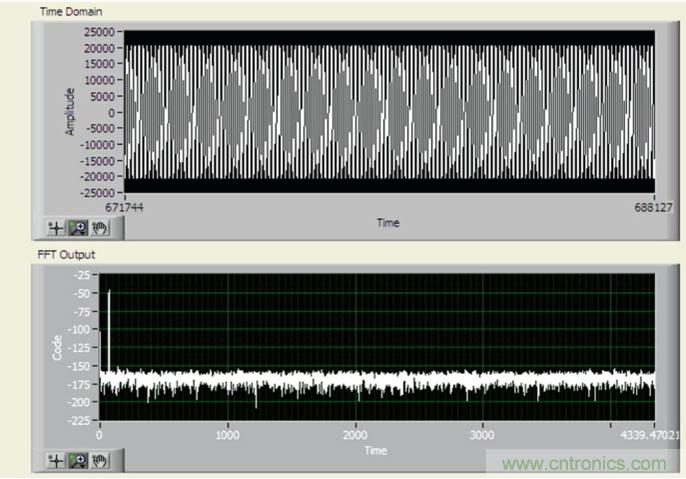

處于G = 100模式時(shí)�����,采用外限值T3和T4�。如果ADC結(jié)果預(yù)計(jì)高于T3或低于T4,增益就會(huì)切換至G = 1模式�,以防止超出ADC輸入的量程(如圖9所示)���。

圖9. 當(dāng)ADC輸入預(yù)計(jì)位于閾值限值以外時(shí),從放大器輸入到轉(zhuǎn)換器輸入的增益減少100(藍(lán)線:放大器輸入����;紅線:轉(zhuǎn)換器輸入。)

當(dāng)處于G = 100模式時(shí)��,如果算法預(yù)測下一個(gè)ADC樣本剛好落在外閾值以外(采用非?�;镜木€性預(yù)測)�����,產(chǎn)生的ADC結(jié)果為+32510���,增益就會(huì)切換到G = 1�,下一個(gè)ADC輸出結(jié)果就不是+32510����,而是+325。

在類似的系統(tǒng)中����,要想防止震顫(閾值附近快速反復(fù)的增益切換), 則須使用遲滯 (100至1和1至100切換電平的分離) 它對(duì)確定正確的閾值限值十分重要���。在本例采用的實(shí)際限值的計(jì)算中,設(shè)置了明顯的遲滯�����。如果系統(tǒng)從高增益(G = 100)模式切換到低增益(G = 1)模式����,系統(tǒng)的模擬輸入電壓就必須減少約50%才能返回到高增益模式。

整個(gè)系統(tǒng)的性能

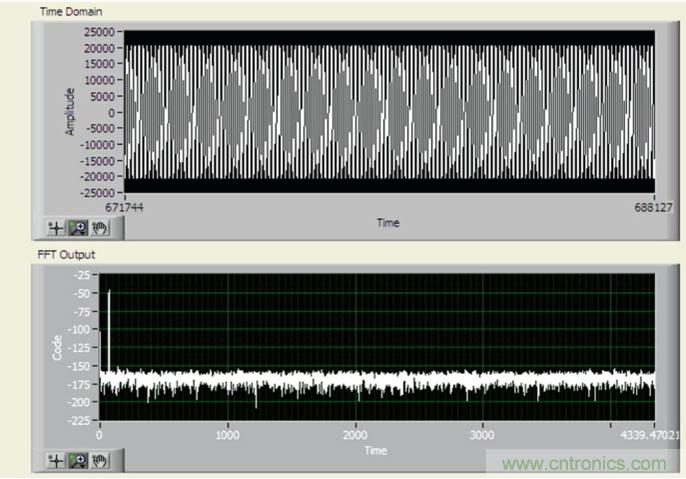

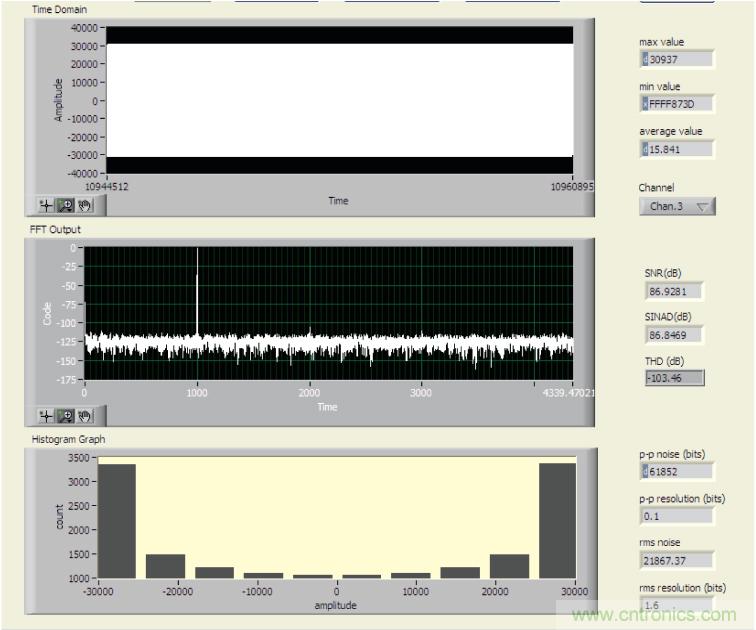

獲得充分優(yōu)化的增益和抽取算法后���,整個(gè)系統(tǒng)就準(zhǔn)備就緒�,可以開始測試���。圖10顯示了系統(tǒng)對(duì)運(yùn)行在1 kHz下的–0.5 dBFS大信號(hào)輸入音作出的響應(yīng)。將100的PGA增益考慮在內(nèi)時(shí)����,實(shí)現(xiàn)的動(dòng)態(tài)范圍為127 dB。

圖10. 對(duì)大量程1 kHz信號(hào)的響應(yīng)

與此類似��,當(dāng)針對(duì)圖11中的小信號(hào)輸入進(jìn)行測試�����,且輸入音在–46.5 dBFS下為70 Hz時(shí),實(shí)現(xiàn)的動(dòng)態(tài)范圍可達(dá)129 dB�����。較小輸入音的性能有望得到提升��,因?yàn)樵摐y量過程中沒有發(fā)生增益范圍的有源切換�����。

圖11. 70 Hz時(shí)對(duì)小量程輸入信號(hào)的響應(yīng)

結(jié)束語

系統(tǒng)的性能取決于其能否動(dòng)態(tài)地切換增益以處理大小兩種信號(hào)輸入���。∑-?技術(shù)能夠提供出色的動(dòng)態(tài)范圍��,而逼近型解決方案則可以根據(jù)輸入信號(hào)動(dòng)態(tài)改變前端增益��,不會(huì)影響系統(tǒng)的性能�����。小信號(hào)和大信號(hào)交流和直流輸入都可以實(shí)時(shí)測量��,無需等待系統(tǒng)建立時(shí)間���,也不會(huì)由于延遲增益改變而產(chǎn)生較大的突波�����。

系統(tǒng)的關(guān)鍵是結(jié)合ADC過采樣技術(shù)與預(yù)見性增益設(shè)置算法��。如何處理輸入信號(hào)的壓擺率對(duì)于增益算法至關(guān)重要��。輸入壓擺率較高時(shí)��,可能需要定制增益設(shè)置�����,以便當(dāng)信號(hào)接近可能超出ADC輸入量程的電平時(shí)�����,快速做出響應(yīng)。這一要求可以通過縮小閾值來實(shí)現(xiàn)���,或者用多個(gè)樣本取代兩個(gè)樣本��,通過對(duì)輸入信號(hào)進(jìn)行更復(fù)雜的預(yù)測分析來實(shí)現(xiàn)��,如本例所述�����。反之��,在輸入壓擺率極低的系統(tǒng)中�,可以擴(kuò)大閾值,從而更好地使用高增益模式�����,而不會(huì)超出ADC輸入量程���。

雖然本文介紹的是AD7985 ADC����,但所用的技術(shù)同樣適用于ADI公司的其他高速轉(zhuǎn)換器����。采用更快的ADC采樣速率后,最終用戶可以將增加的輸入帶寬和更快的輸出數(shù)據(jù)轉(zhuǎn)變?yōu)樵黾拥倪^采樣率�����,從而實(shí)現(xiàn)更大的動(dòng)態(tài)范圍。

如果采用AD8253 VGA的額外增益范圍����,而不僅僅是G = 1和G = 100,可以進(jìn)一步減小增益變化的影響����。在本文所述的示例中,增益切換時(shí)會(huì)產(chǎn)生少量的失真�。但是,如果采用G= 10的范圍��,對(duì)采用額外校準(zhǔn)點(diǎn)的三步進(jìn)增益而言����,可能會(huì)實(shí)現(xiàn)更好的系統(tǒng)THD參數(shù)。

推薦閱讀: