【導(dǎo)讀】按照產(chǎn)品在電磁兼容設(shè)計(jì)時(shí)所采取的各項(xiàng)措施的重要性為先后,分為若干層次進(jìn)行設(shè)計(jì),并加以綜合分析進(jìn)行適當(dāng)調(diào)整直到完善,這就是本文提出的” 電磁兼容分層與綜合設(shè)計(jì)法”??梢宰龅诫姶偶嫒菰囼?yàn)一次成功。

人們?cè)谘邪l(fā)新產(chǎn)品時(shí),往往急于實(shí)現(xiàn)產(chǎn)品的功能,于是沿用低頻、低速時(shí)的經(jīng)驗(yàn),滿足于利用軟件將單片機(jī)、芯片和元器件連接起來(lái),就希望實(shí)現(xiàn)產(chǎn)品功能、效能和性能,結(jié)果事與愿違,不僅只是在低水平徘徊,而且延誤了寶貴的時(shí)間。

其實(shí),隨著集成電路時(shí)鐘速率的提高,上升、下降沿速率加快,電源電壓降低以及產(chǎn)品復(fù)雜性和密集度的提高、設(shè)計(jì)周期的不斷縮短,沿用低頻、低速時(shí)的經(jīng)驗(yàn)已完全不能實(shí)現(xiàn)產(chǎn)品的功能、效能和性能。如果在產(chǎn)品設(shè)計(jì)的后期重新設(shè)計(jì),則成本很高。如果延誤日期,損失就更大。

因此,“第一時(shí)間推出產(chǎn)品”的設(shè)計(jì)目標(biāo),是生死攸關(guān)的競(jìng)爭(zhēng)需要。要在第一時(shí)間實(shí)現(xiàn)產(chǎn)品規(guī)定功能、使產(chǎn)品效能得以充分發(fā)揮,并達(dá)到最高性能,就必須做好EMC設(shè)計(jì)。為了以最低的成本解決EMC問題,就必須在功能設(shè)計(jì)的同時(shí),進(jìn)行EMC設(shè)計(jì),并選用正確的方法。

現(xiàn)在,產(chǎn)品設(shè)計(jì)的重點(diǎn)已從功能設(shè)計(jì)和邏輯設(shè)計(jì),轉(zhuǎn)移到EMC設(shè)計(jì)上來(lái)了。

進(jìn)行電磁兼容設(shè)計(jì)的正確方法,應(yīng)做到:標(biāo)本兼治,重在治本。 就是從治理電磁兼容問題的源頭出發(fā),按重要性為先后,分為若干層次進(jìn)行設(shè)計(jì),并加以綜合分析,進(jìn)行適當(dāng)調(diào)整,直到完善:

- 第一層為重在治本之一:有源器件的選型和印刷電路板設(shè)計(jì)

- 第二層為重在治本之二:接地設(shè)計(jì)

- 第三層為標(biāo)本兼治之一:結(jié)構(gòu)/屏蔽設(shè)計(jì)

- 第四層為標(biāo)本兼治之二:濾波設(shè)計(jì)

- 第五層為標(biāo)本兼治之三:瞬態(tài)騷擾抑制設(shè)計(jì)

- 第六層為系統(tǒng)級(jí)電磁兼容設(shè)計(jì)

并且在每一層進(jìn)行接地、屏蔽和濾波的綜合設(shè)計(jì)和軟件抗騷擾設(shè)計(jì)。這就稱為“電磁兼容分層與綜合設(shè)計(jì)法”。可以做到電磁兼容試驗(yàn)一次成功。

“電磁兼容分層與綜合設(shè)計(jì)法” 是本文作者在2000年5月“全國(guó)電磁兼容標(biāo)準(zhǔn)與質(zhì)量認(rèn)證研討會(huì)”上,首次提出,至今已十余年。在全國(guó)推廣十余年以來(lái), 一批企業(yè)先后走出”測(cè)試修改法”導(dǎo)致電磁兼容試驗(yàn)失敗的“怪圈”,做到在產(chǎn)品設(shè)計(jì)之初,就主動(dòng)進(jìn)行電磁兼容設(shè)計(jì)。而且,電磁兼容設(shè)計(jì)的投入僅需1% (國(guó)內(nèi)一般為5%至10%)。既降低了成本,又縮短了研發(fā)時(shí)間。同時(shí),也使“電磁兼容分層與綜合設(shè)計(jì)法”更加充實(shí)與完善,得到了全國(guó)許多企業(yè)和單位的認(rèn)可。

第一層 有源器件的選型和印刷電路板設(shè)計(jì)

在電磁兼容問題的源頭,根本上解決EMC問題,必須首先做好芯片的選型和印刷電路板設(shè)計(jì)。

一.有源器件的敏感度特性與發(fā)射特性

1. 電磁敏感度特性

模擬器件帶內(nèi)敏感度特性取決于靈敏度和帶寬;帶外敏感度特性用帶外抑制特性表示。

邏輯器件帶內(nèi)敏感度特性取決于噪聲容限或噪聲抗擾度,帶外敏感度特性也是用帶外抑制特性表示。

2.電磁發(fā)射特性

邏輯器件是一種騷擾發(fā)射較強(qiáng)的最常見的寬帶騷擾源。時(shí)鐘波形的上升時(shí)間tr 越短,對(duì)應(yīng)邏輯脈沖所占帶寬越寬

BW=1/ptr

此帶寬也是最高頻率分量。實(shí)際輻射頻率范圍可能達(dá)到BW的十倍以上。通過(guò)器件手冊(cè)可以查出tr的典型值。

人們普遍認(rèn)為:在PCB設(shè)計(jì)中,需要考慮的關(guān)鍵問題是時(shí)鐘頻率,其實(shí),時(shí)鐘波形的上升時(shí)間tr才是最關(guān)鍵的因素。上升時(shí)間tr定義為從波形的10%處上升到90%處所需要的時(shí)間。如果在互連線的一端輸入方波,要求在另一端也得到方波,則該互連線不僅必須能傳輸方波的基波,還必須能傳輸全部高次諧波,至少為15次諧波。這就是說(shuō),PCB的時(shí)鐘頻率并不重要,上升時(shí)間tr和需要重新產(chǎn)生的諧波才是最重要的。描述這個(gè)要求的詞語(yǔ)就是帶寬BW,也即最高頻率分量。

3. △I 噪聲電流、瞬態(tài)負(fù)載電流IL的產(chǎn)生和危害

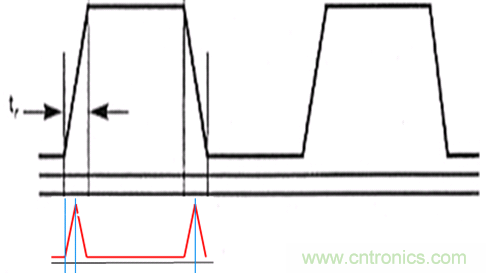

當(dāng)數(shù)字集成電路在加電工作時(shí),它內(nèi)部的門電路將會(huì)發(fā)生 “0”和“1”的變換,即開關(guān)狀態(tài)。在變換的過(guò)程中,該門電路中的晶體管將發(fā)生導(dǎo)通和截止?fàn)顟B(tài)的轉(zhuǎn)換,會(huì)有瞬間變化電流-浪涌電流di/dt從所接電源流入門電路,或從門電路流入地線,這個(gè)變化電流就是△I噪聲的初始源,稱△I噪聲電流。如圖1所示。

圖1 △I噪聲電流

設(shè)驅(qū)動(dòng)線對(duì)地電容與驅(qū)動(dòng)門輸入電容之和為負(fù)載電容 Cs,平時(shí)被充電,其值為電源電壓。驅(qū)動(dòng)門由高電位翻轉(zhuǎn)為低電位時(shí)Cs放電,放電電流稱為瞬態(tài)負(fù)載電流:

IL = Cs×dv/dt

瞬態(tài)負(fù)載電流IL與△I噪聲電流復(fù)合后,會(huì)產(chǎn)生更強(qiáng)的電磁騷擾發(fā)射。是阻礙實(shí)現(xiàn)產(chǎn)品規(guī)定功能、使產(chǎn)品效能得不到充分發(fā)揮的主要原因.由于PCB上,信號(hào)線、電源線和地線等都存在一定的引線電感L,瞬態(tài)負(fù)載電流IL與△I噪聲電流復(fù)合后產(chǎn)生的瞬間變化電流di/dt,將通過(guò)引線電感L的感抗引起尖峰電壓

V= - Ldi/dt

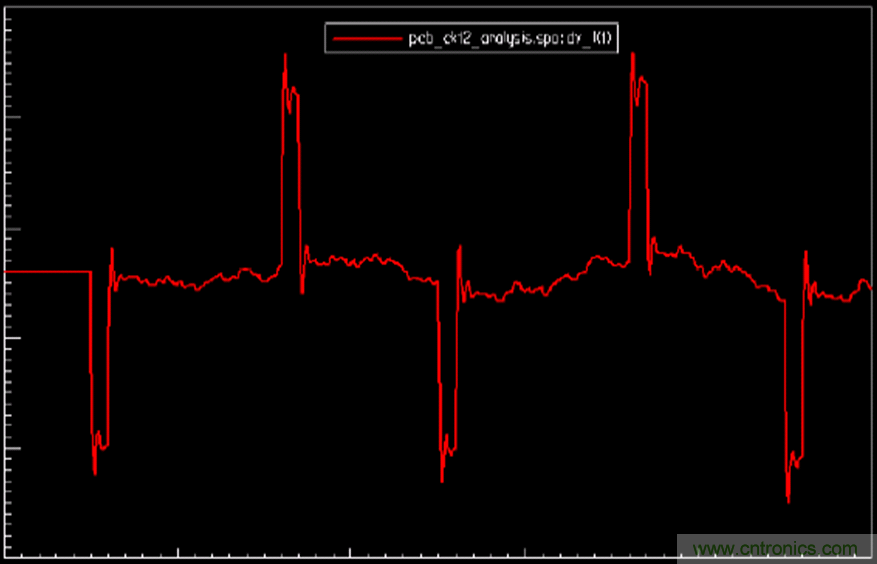

即△I噪聲電壓,稱為同步開關(guān)噪聲(Simultaneous Switch Noise SSN),如圖2所示,會(huì)引發(fā)地電位和電源電壓的波動(dòng)(Ground/Power Bounce),產(chǎn)生電磁騷擾發(fā)射。所以,引線電感L是產(chǎn)生傳導(dǎo)騷擾和輻射騷擾的根源之一。

圖2 尖峰電壓

電磁騷擾發(fā)射的另一根源為等效電壓源的源阻抗,也即電源分配系統(tǒng)輸入阻抗Z,系統(tǒng)要求尖峰電壓應(yīng)在正常電源電壓的±2.5%至±5%以內(nèi)。等效于源阻抗Z要足夠低

V= Z×ΔI

不論ΔI如何變化,都可保持V變化很小。這可通過(guò)安裝去耦電容達(dá)到。

理想電源的源阻抗Z為零,電源平面上任何一點(diǎn)電位保持恒定。

4.掌握IC設(shè)計(jì)和封裝特性抑制EMI

IC封裝也是產(chǎn)生電磁騷擾的原因之一。 IC封裝包括芯片,內(nèi)部PCB以及焊盤。直接影響IC封裝的電容和電感。

芯片是作為系統(tǒng)的一部分而存在的,硅芯片必須采用某種封裝,然后焊接到PCB板上。 這一互連鏈,即芯片通過(guò)封裝連接到PCB板上,本身就是一個(gè)復(fù)雜系統(tǒng)。

應(yīng)將芯片設(shè)計(jì)、封裝和印刷電路板作為一個(gè)系統(tǒng)來(lái)考慮。以保證最后組裝和加電后能得到所期望的結(jié)果。最好的方法是,對(duì)所有這些進(jìn)行并行設(shè)計(jì)、分析和驗(yàn)證。

封裝是指安裝半導(dǎo)體集成電路芯片用的外殼,它不僅起著安放,固定,密封,保護(hù)芯片和增強(qiáng)電熱性能的作用,而且還是溝通芯片內(nèi)部世界與外部電路的橋梁--芯片上的接點(diǎn)用導(dǎo)線連接到封裝外殼的引腳上,這些引腳又通過(guò)印制板上的導(dǎo)線與其它器件建立連接。衡量一個(gè)芯片封裝技術(shù)先進(jìn)與否的重要指標(biāo)是芯片面積與封裝面積之比,這個(gè)比值越接近1越好,引線電感越小。封裝技術(shù)已經(jīng)歷了好幾代的變遷:

1)通孔插入式封裝(Through-hole Package)

DIP(Dual In-line Package) 雙列直插式封裝:上世紀(jì) 70年代的封裝,最大引腳數(shù)64條。其芯片面積/封裝面積為1:8.6,離1相差很遠(yuǎn),說(shuō)明封裝效率很低,引線很長(zhǎng),引線電感很大;

PGA(Pin Grid Array)針柵陣列式封裝,引腳中心距為2.54mm,引腳數(shù)為64-447。表面安裝式PGA引腳中心距為1.27mm,引腳數(shù)為250-528,引線電感很大;

2)表面安裝式封裝(Surface Mounted Package )

上世紀(jì)80年代出現(xiàn)了芯片載體封裝,有陶瓷無(wú)引線芯片載體封裝LCCC,塑料有引線芯片載體封裝PLCC,小尺寸封裝SOP(Small Outline Package),塑料四邊引出扁平封裝PQFP。芯片面積/封裝面積為1:7.8,引線電感仍很大;

3)BGA封裝與CSP封裝

上世紀(jì)90年代隨著集成技術(shù)的進(jìn)步和深亞微米技術(shù)的使用,LSI,VLSI,ULSI相繼出現(xiàn),芯片集成度不斷提高,對(duì)封裝要求更加嚴(yán)格,I/O引腳數(shù)急劇增加,功耗也隨之增大。為滿足發(fā)展的需要,在原有封裝品種基礎(chǔ)上,又增添了新的品種--球柵陣列封裝簡(jiǎn)稱BGA(Ball Grid Array Package)。成為CPU南北橋等VLSI芯片的高密度,高性能,多功能及高I/O引腳封裝的最佳選擇。芯片面積/封裝面積為1:4,引線電感有所減??;1994年9月誕生了一種新的封裝形式命名為芯片尺封裝,CSP(Chip Size Package或ChipScale Package),芯片面積/封裝面積為1:1.1。也就是說(shuō),單個(gè)芯片有多大,封裝尺寸就有多大,引線電感大大減??;

4)裸芯片組裝

隨著組裝密度和IC的集成度的不斷提高,為適應(yīng)這種趨勢(shì),IC的裸芯片組裝形式應(yīng)運(yùn)而生,并得到廣泛應(yīng)用。它是從已完工的晶圓(Water)上切下的芯片,不按傳統(tǒng)之 IC 先行封裝成體,而將芯片直接組裝在電路板上,謂之 Bare Chip Assembly。早期的 COB (Chip on Board)做法就是裸芯片的具體使用,不過(guò) COB 是將芯片的背面黏貼在板子上,再行引線及膠封。而新一代的 Bare Chip 卻連引線也省掉,是以芯片正面的各電極點(diǎn),直接反扣熔焊在板面各配合點(diǎn)上( Flip Chip)?;蛞孕酒耐箟K扣接在載帶自動(dòng)鍵合(TAB)的內(nèi)腳上,再以其外腳連接在 PCB 上。此二種新式組裝法皆稱為 裸芯片組裝,寄生 C,L小.并且可節(jié)省整體成本約 30% 左右;

5)載帶自動(dòng)鍵合(TAB):多接腳大型芯片組裝:裸芯片貼裝技術(shù)之一

載帶基材為聚酰亞胺薄膜,表面覆蓋上銅箔后,用化學(xué)法腐蝕出精細(xì)的引線圖形。芯片在引出點(diǎn)上鍍Au、Cu或Sn/Pn合金,形成高度為20-30mm的凸點(diǎn)電極。組裝方法是將芯片粘貼在載帶上,將凸點(diǎn)電極與載帶的引線連接,然后用樹脂封裝。它適用于大批量自動(dòng)化生產(chǎn)。TAB的引線間距可較QFP進(jìn)一步縮小至0.2mm或更短。

6)系統(tǒng)芯片(SoC)

SoC就是將系統(tǒng)的全部功能模塊集成到單一半導(dǎo)體芯片上. 將一片SoC與現(xiàn)在的板卡相比,其中可能含有的功能模塊有:CPU、RAM、ROM、DSP、無(wú)線模塊、模擬和數(shù)字模塊、網(wǎng)絡(luò)模塊、硬核等。

嵌入式片上系統(tǒng)將整個(gè)嵌入式系統(tǒng)集成到一塊芯片中,應(yīng)用系統(tǒng)的電路板變得簡(jiǎn)潔,減小體積和功耗,提高了可靠性。而且,通過(guò)改變內(nèi)部工作電壓,降低芯片功耗;減少芯片對(duì)外引腳數(shù),簡(jiǎn)化制造過(guò)程;減少外圍驅(qū)動(dòng)接口單元與電路板之間的信號(hào)傳遞,加快數(shù)據(jù)處理速度;內(nèi)嵌線路可避免外部電路板在信號(hào)傳遞時(shí)所造成的騷擾。

單芯片嵌入式微控制器(MicroController Unit,MCU)俗稱單片機(jī),將整個(gè)嵌入式微計(jì)算機(jī)系統(tǒng)集成到一塊芯片中,從而使功耗和成本下降,可靠性提高。

IC產(chǎn)業(yè)技術(shù)發(fā)展經(jīng)歷了電路集成、功能集成、技術(shù)集成,直到今天基于計(jì)算機(jī)軟硬件的知識(shí)集成,其目標(biāo)就是將電子產(chǎn)品系統(tǒng)電路不斷集成到芯片中去,力圖吞噬整個(gè)產(chǎn)品系統(tǒng)。單芯片的嵌入式系統(tǒng)的出現(xiàn),以單個(gè)芯片實(shí)現(xiàn)的產(chǎn)品系統(tǒng)不僅僅限于硬件系統(tǒng),而是一個(gè)帶有柔性性能的軟、硬件集合體的電子系統(tǒng)。SoC是微電子領(lǐng)域IC設(shè)計(jì)的最終目標(biāo).

二.印刷電路板設(shè)計(jì)

隨著信息寬帶化和高速化的發(fā)展,要求信號(hào)的傳輸和處理的速度越來(lái)越快。已經(jīng)成為PCB設(shè)計(jì)必須關(guān)心的問題之一。PCB已不僅僅是支撐電子元器件的平臺(tái),簡(jiǎn)簡(jiǎn)單單在基材上布上金屬導(dǎo)線,由于存在引線電感,并不能能實(shí)現(xiàn)互連。PCB已成為功能元件,成為高性能的系統(tǒng)結(jié)構(gòu)。從而使得PCB設(shè)計(jì)成為產(chǎn)品設(shè)計(jì)能否成功的關(guān)鍵因素。

印制電路板EMC設(shè)計(jì)是產(chǎn)品EMC設(shè)計(jì)的基礎(chǔ).整機(jī)輻射發(fā)射超標(biāo),輻射敏感度不達(dá)標(biāo),大多是由于PCB引起的。

在PCB設(shè)計(jì)階段處理好EMC問題,是使產(chǎn)品實(shí)現(xiàn)電磁兼容最有效,成本最低的手段。

1. 電磁騷擾發(fā)射的抑制方法之一:PCB布線及布局基本原則

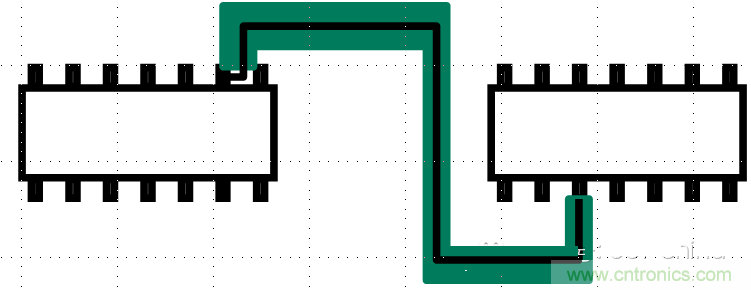

電流必須在一個(gè)回路中流動(dòng)。每個(gè)信號(hào)都有一個(gè)回流來(lái)構(gòu)成回路。直流和低頻時(shí),回路電流總是從電阻最小的路徑上通過(guò);而高頻時(shí),回流總是從阻抗最小的路徑上通過(guò)。

兩根導(dǎo)線分別流過(guò)大小相等方向相反的信號(hào)電流和它的回流電流,它們的磁場(chǎng)也是大小相等方向相反,如果兩根導(dǎo)線距離非常近,磁場(chǎng)即差模EMI輻射將完全抵消。所以基本原則是:如果要把差模EMI輻射減小到最小,信號(hào)線應(yīng)盡量靠近與它構(gòu)成回路的回流線,即必須把回路面積減少到最小。

精心的走線設(shè)計(jì)可以在很大程度上減少走線阻抗造成的騷擾,而抑制電磁騷擾發(fā)射。當(dāng)頻率超過(guò)數(shù)kHz時(shí),導(dǎo)線的阻抗主要由導(dǎo)線的電感決定,細(xì)而長(zhǎng)的回路導(dǎo)線呈現(xiàn)高電感(典型lOnH/cm),其阻抗隨頻率增加而增加。如果設(shè)計(jì)處理不當(dāng),將引起共阻抗耦合。

兩根電流方向相反的平行導(dǎo)線,由于互感作用,能夠有效地減少電感,總自感可表示為:

L = L1 +L2 - 2M

式中, L1、L2分別為導(dǎo)線1和導(dǎo)線2的自感,M為互感

M=L1/[1+(a/h)2]

式中,a—間距, h—離地面距離。當(dāng):L1 = L2,則:

L =2 (L1- M)

當(dāng):a = 0

M = L1

,則 L = 0。

由此可以得到布線基本原則,即環(huán)路面積為零。例如,多層板層間距離很小,4層板為0.15mm,而28層板為0.05mm能真正做到環(huán)路面積為零,總自感為零,如圖3所示。

圖3 布線基本原則:環(huán)路面積為零

在印制板布局時(shí),應(yīng)先進(jìn)行物理分區(qū)和電氣分區(qū),確定元器件在板上的位置,然后布置地線、電源線,再安排高速信號(hào)線,最后考慮低速信號(hào)線。

布局時(shí),首先作好不兼容分割,元器件的位置應(yīng)按電源電壓、數(shù)字及模擬電路、速度快慢、電流大小等進(jìn)行分組,以免相互騷擾。根據(jù)元器件的位置可以確定印制板連接器各個(gè)引腳的安排。所有連接器應(yīng)安排在印制板的一側(cè),盡量避免從兩側(cè)引出電纜,減少共模輻射。其次,在安裝,受力,受熱和美觀等方面應(yīng)滿足要求。

(1)電源線

在考慮安全條件下,電源線應(yīng)盡可能靠近地線, 以減小差模輻射的環(huán)面積,也有助于減小電路的交擾。對(duì)于單一電源供電的PCB,一個(gè)電源平面足夠了;對(duì)于多種電源,若互不交錯(cuò),可考慮采取電源層分割,用作參考面時(shí),需加縫補(bǔ)電容;對(duì)于電源互相交錯(cuò)(尤其多種電源供電,且互相交錯(cuò)的IC)的單板,則必須考慮采用2個(gè)或以上的電源平面。

(2)時(shí)鐘線、信號(hào)線和地線的位置

時(shí)鐘線、信號(hào)線與地平面相鄰或與地線距離較近,形成的環(huán)路面積盡量小。必要時(shí),兩側(cè)加地線護(hù)送。

(3)按邏輯速度分割

當(dāng)需要在電路板上布置快速、中速和低速邏輯電路時(shí),高速的器件(快邏輯、時(shí)鐘振蕩器等)應(yīng)安放在緊靠邊緣連接器范圍內(nèi),而低速邏輯和存儲(chǔ)器,應(yīng)安放在遠(yuǎn)離連接器范圍內(nèi)。這樣對(duì)共阻抗耦合、輻射和交擾的減小都是有利的。

(4)避免印制電路板導(dǎo)線特性阻抗的不連續(xù)性,保證特性阻抗連續(xù),必須做到跡線寬度不要突變、導(dǎo)線不要突然拐角,同層的佈線的寬度必須連續(xù),不同層的走線阻抗也必須連續(xù)。

(5)檢查信號(hào)線的長(zhǎng)度和信號(hào)的頻率是否構(gòu)成諧振,即當(dāng)佈線長(zhǎng)度為信號(hào)波長(zhǎng)1/4的時(shí)候的整數(shù)倍時(shí),此佈線將產(chǎn)生諧振,而諧振就會(huì)輻射電磁波,產(chǎn)生騷擾。

2. 高速數(shù)字電路設(shè)計(jì)

在電子系統(tǒng)中,需要各種長(zhǎng)度的走線。在這些走線上,信號(hào)從線的始端傳輸?shù)浇K端,需要一定時(shí)間。也就是說(shuō),信號(hào)存在延時(shí)。這種延時(shí),在低速系統(tǒng)中可以忽略;但在高速系統(tǒng)中,則不能被忽略。高速PCB設(shè)計(jì)還需考慮當(dāng)信號(hào)在導(dǎo)線上傳輸時(shí),如果傳輸線與始端阻抗或終端阻抗不匹配,將會(huì)出現(xiàn)電磁波反射現(xiàn)象,使信號(hào)失真,產(chǎn)生干擾脈沖,影響系統(tǒng)運(yùn)行。

所謂高速PCB,是從數(shù)字電路的角度說(shuō)的,而對(duì)于模擬電路的PCB,則是高頻問題。高速指的是信號(hào)的邊緣速率高,而不一定是時(shí)鐘頻率高,可以這么說(shuō):時(shí)鐘頻率低的PCB,不一定不是高速PCB,而時(shí)鐘頻率高的PCB,則一定也是高速PCB。一旦把所設(shè)計(jì)的PCB當(dāng)作高速PCB來(lái)設(shè)計(jì)后,就需要考慮高速信號(hào)的傳輸、端接、串?dāng)_等問題,如果不這樣考慮,不進(jìn)行高速信號(hào)的完整性設(shè)計(jì),PCB的工作可靠性可能就不能保證,甚至無(wú)法正常工作。而對(duì)于普通PCB,不去考慮高速的影響,則沒有關(guān)系。

信號(hào)完整性(Signal Integrity,簡(jiǎn)稱SI)是指在信號(hào)線上的信號(hào)質(zhì)量及信號(hào)定時(shí)的準(zhǔn)確性。即在要求的時(shí)間內(nèi),信號(hào)能以要求的時(shí)序、持續(xù)時(shí)間和電壓幅度作出響應(yīng),不失真的從源端傳送到接收端,則該信號(hào)是完整的。所以,信號(hào)完整性分析是以電壓波形為主的分析。

時(shí)序是高速系統(tǒng)的核心問題。如果定時(shí)不準(zhǔn)確,則不能得到準(zhǔn)確的邏輯。信號(hào)傳輸時(shí),任何發(fā)生在驅(qū)動(dòng)端,互連線或接收端的延時(shí)或波形畸變都會(huì)導(dǎo)致傳輸失敗。

破壞信號(hào)完整性的原因有:所使用的芯片切換速度過(guò)快;端接元件布設(shè)不合理、電路互連不合理以及傳輸線、過(guò)孔等引起的阻抗不連續(xù);線距過(guò)小引起的串?dāng)_以及尖峰電壓等都會(huì)引起信號(hào)完整性問題。信號(hào)完整性問題包括反射、串?dāng)_、過(guò)沖、振蕩、時(shí)延和電磁騷擾發(fā)射等。信號(hào)完整性分析的目標(biāo)是保證可靠的高速數(shù)據(jù)傳輸.高速數(shù)字系統(tǒng)設(shè)計(jì)成功的關(guān)鍵在于保持信號(hào)的完整性。從廣義上講,信號(hào)完整性問題指的是在高速產(chǎn)品中,互連線引起的所有問題。它主要研究互連線與數(shù)字信號(hào)電壓電流波形相互作用時(shí),如何影響產(chǎn)品性能。信號(hào)完整性問題包括:

- 反射信號(hào)Reflected signals

- 延時(shí)和時(shí)序錯(cuò)誤Delay & Timing errors

- 過(guò)沖與下沖Overshoot/Undershoot

- 振鈴Ringing(多次跨越邏輯電平門限錯(cuò)誤False switching )

- 串?dāng)_Induced Noise (or crosstalk)

- 電磁輻射EMI radiation

為了實(shí)現(xiàn)信號(hào)完整性,必須縮短 S 并進(jìn)行阻抗匹配,阻抗匹配方法有:串聯(lián)電阻、并聯(lián)電阻、戴維南網(wǎng)絡(luò)、RC網(wǎng)絡(luò)、二極管陣等。

第二層 接地設(shè)計(jì)

一.接地設(shè)計(jì)是重在治本的重要一層。

1.接地是指將一個(gè)電路、設(shè)備、分系統(tǒng)與參考地連接,目的在于提供一個(gè)等電位點(diǎn)或面。接地必須有接地導(dǎo)體和參考地才能完成。

2.參考地的含義是廣泛的,可以是大地,也可以是起大地作用的,有足夠面積的導(dǎo)體。如飛機(jī)或船舶的殼體,機(jī)柜的柜體等。理想的參考地是一個(gè)零電位、零阻抗的物理體。能為電路或系統(tǒng)提供基準(zhǔn)電位;能抑制產(chǎn)品內(nèi)部產(chǎn)生的電磁騷擾以及外部進(jìn)入產(chǎn)品的電磁騷擾;并能為電流流回源提供一條低阻抗路徑。

3接地是一個(gè)系統(tǒng)概念。電流幅值和頻率是兩項(xiàng)關(guān)鍵因素。對(duì)接地分類是為了選擇接地體及其連接方式。

- 接地分類 接地電流幅值 接地電流頻率范圍

- 信號(hào)地 (回流地) 幾mA-幾A 直流-GHz

- 電源地 幾mA-幾A <50-60Hz

- 保護(hù)地 (安全地) 10A-1000A <50-60Hz

- 防雷地 <240kA 200kHz-500MHz

- 參考地 (EMI地) μA-A 直流-微波

參考地任務(wù)之一是為EMI電流提供一個(gè)受控抑制通道。關(guān)鍵是在極寬的頻率范圍內(nèi)保持低阻抗。

防雷地是提供一條將雷電電流通入大地的受控通道。關(guān)鍵是同時(shí)維持低電阻和低電感,并且提供充分的瞬態(tài)電流容量。

安全地(保護(hù)地 )主要是為了保護(hù)人身安全。通常將金屬殼體接地,出現(xiàn)故障時(shí)確保故障電流流入大地。

電源地的主要問題是維持低阻抗,并提供足夠的電流容量。

信號(hào)地(回流地)為信號(hào)提供一個(gè)回流通道

二.接地方式

1.懸浮地

信號(hào)電平較大或接近時(shí),該模塊應(yīng)接系統(tǒng)地,信號(hào)電平較小或相差大時(shí),低電平信號(hào)模塊應(yīng)接懸浮地。

設(shè)備懸浮地設(shè)備的地線在電氣上與參考地及其他導(dǎo)體相絕緣

單元電路懸浮地單元電路信號(hào)地與參考地及機(jī)箱絕緣

懸浮地容易產(chǎn)生靜電積累和靜電放電。易遭雷擊和其他瞬態(tài)騷擾。通常在懸浮地與參考地之間接進(jìn)一個(gè)阻值很大的電阻以消除靜電積累。

2. 單點(diǎn)接地(f<1MHz)

并聯(lián)單點(diǎn)接地:每個(gè)電路模塊都接到一個(gè)單點(diǎn)地上,每個(gè)單元在同一點(diǎn)與參考點(diǎn)相連。

多級(jí)電路的串聯(lián)單點(diǎn)接地:接地點(diǎn)應(yīng)選在低電平電路的輸入端,使其最接近參考地。若把接地點(diǎn)移到高電平端,則 輸入級(jí)的地對(duì)參考地的電位差最大,是不穩(wěn)定的。

3. 多點(diǎn)接地(f >10MHz)

設(shè)備中的電路都就近以機(jī)殼為參考點(diǎn),而所有機(jī)殼又以地為參考,使接地引線長(zhǎng)度最短。在多點(diǎn)接地的情況下,要注意地環(huán)路問題。信號(hào)頻率在1-10MHz之間,當(dāng)?shù)鼐€長(zhǎng)度不超過(guò)l /20時(shí),可以采用單點(diǎn)接地,否則就要多點(diǎn)接地。當(dāng)?shù)鼐€長(zhǎng)度可以與l/4相比擬時(shí),成為終端短路的l/4傳輸線,等效為開路,阻抗增大。

4. 混合接地

使用電抗元件使接地系統(tǒng)在低頻和高頻時(shí)呈現(xiàn)不同特性。

電子設(shè)備的混合接地把設(shè)備的地線分成兩類:電源地與信號(hào)地。設(shè)備中各部分電源地線都接到電源總地線上與信號(hào)總地線匯集到公共參考地。

三.長(zhǎng)地線的阻抗

1.地線阻抗是導(dǎo)致地線騷擾的根本原因

理想地線應(yīng)是一個(gè)零電位、零阻抗的物理實(shí)體。但實(shí)際的地線本身既有電阻分量又有電抗分量,當(dāng)有電流通過(guò)該地線時(shí),就要產(chǎn)生電壓降。地線會(huì)與其他連線(信號(hào)、電源線等)構(gòu)成回路,當(dāng)時(shí)變電磁場(chǎng)耦合到該回路時(shí),就在地回路中產(chǎn)生感應(yīng)電動(dòng)勢(shì),并由地回路耦合到負(fù)載,構(gòu)成潛在的EMI威脅。

傳輸線輸入阻抗

Zin(x)=Zc(ZL+jZctgβx)/(Zc+jZLtgβx)

式中,β=2π/λ=ω(LC)1/2,

當(dāng) ZL=0

∣Zin(x)∣=∣jZctgβx∣=Zctg(ωx(LC)1/2)

當(dāng) x=λ/4

∣Zin(x)∣=Zctg[ω(λ/4)(LC)1/2]=Zctg(π/2)=∞

這時(shí),接地線實(shí)際上開路,反而成為向外輻射的天線

2地線長(zhǎng)度

地線長(zhǎng)度應(yīng)為: ≤l/20 應(yīng)當(dāng)短而粗。

第三層 結(jié)構(gòu) / 屏蔽設(shè)計(jì)

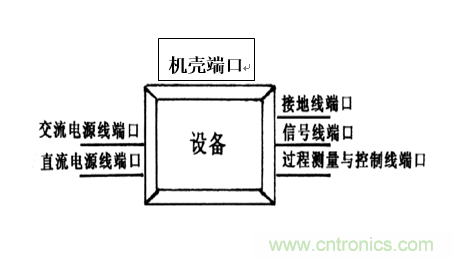

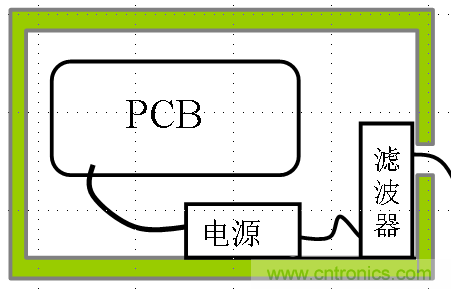

產(chǎn)品電磁兼容設(shè)計(jì)應(yīng)做到標(biāo)本兼治。產(chǎn)品與外界的連接界面,如圖4所示。包括機(jī)殼端口,電源線端口,地線端口,信號(hào)線端口和控制線端口等。需要做好結(jié)構(gòu)/屏蔽設(shè)計(jì),濾波設(shè)計(jì)和瞬態(tài)騷擾抑制設(shè)計(jì)等。

圖4產(chǎn)品與外界的連接界面

什么是結(jié)構(gòu)?結(jié)構(gòu)即材料、形狀、連接、布局的總和。

對(duì)單一零件來(lái)說(shuō),結(jié)構(gòu)即零件的材料和形狀。材料包含零件的內(nèi)在結(jié)構(gòu);形狀體現(xiàn)零件外在特征。

對(duì)兩個(gè)和兩個(gè)以上零件來(lái)說(shuō),還包括他們間的連接方式,“連接”即零件間的裝配方法。

對(duì)整機(jī)來(lái)說(shuō),還要考慮零部件的布局。

結(jié)構(gòu)設(shè)計(jì)通過(guò)設(shè)想和計(jì)算,用工程圖紙或參數(shù)化電子文檔表達(dá)出來(lái),提交制造,實(shí)現(xiàn)產(chǎn)品生產(chǎn)。包括整機(jī)造型、布局、零部件連接、材料和標(biāo)準(zhǔn)件及通用件選擇等。

電子產(chǎn)品結(jié)構(gòu)與純機(jī)械結(jié)構(gòu)的不同之處在于還要考慮結(jié)構(gòu)的電磁兼容性。

屏蔽技術(shù)用來(lái)抑制10kHz以上電磁騷擾沿空間的傳播,即切斷輻射騷擾的耦合途徑。

一.屏蔽效能的概念

用于電磁兼容目的的屏蔽體,通常能將電磁騷擾的強(qiáng)度衰減到原來(lái)的百分之一至百萬(wàn)分之一以上.為了方便起見,屏蔽體的性能以屏蔽效能SE或SH(dB)表示。定義為: SE=20lg(E1/E2)(dB)

SH=20lg(H1/H2)(dB)

式中,E1、H1分別為未屏蔽時(shí)測(cè)得的電場(chǎng)強(qiáng)度和磁場(chǎng)強(qiáng)度, E2、H2分別為屏蔽后測(cè)得的電場(chǎng)強(qiáng)度和磁場(chǎng)強(qiáng)度。

屏蔽體的總體屏蔽效能是由屏蔽體中最薄弱的環(huán)節(jié)決定的。要使屏蔽體的屏蔽效能達(dá)到某一個(gè)值,屏蔽體上所有部位都要達(dá)到這個(gè)值,即各部位屏蔽效能的匹配是十分重要的。

屏蔽體中最薄弱的環(huán)節(jié)是各種縫隙和孔洞。

實(shí)現(xiàn)屏蔽,首先要做好“電磁兼容分層與綜合設(shè)計(jì)法”的第一和第二層,將電磁發(fā)射降至最低,將抗擾能力提至最高。然后利用殼體切斷EMI輻射。

但是,用這個(gè)定義只能測(cè)試屏蔽體的屏蔽效能,而無(wú)法確定應(yīng)該使用什么材料制造屏蔽體。要確定應(yīng)該使用什么材料制造屏蔽體,需要知道材料的屏蔽效能與材料的什么參數(shù)有關(guān)。

1 實(shí)心材料屏蔽效能的計(jì)算

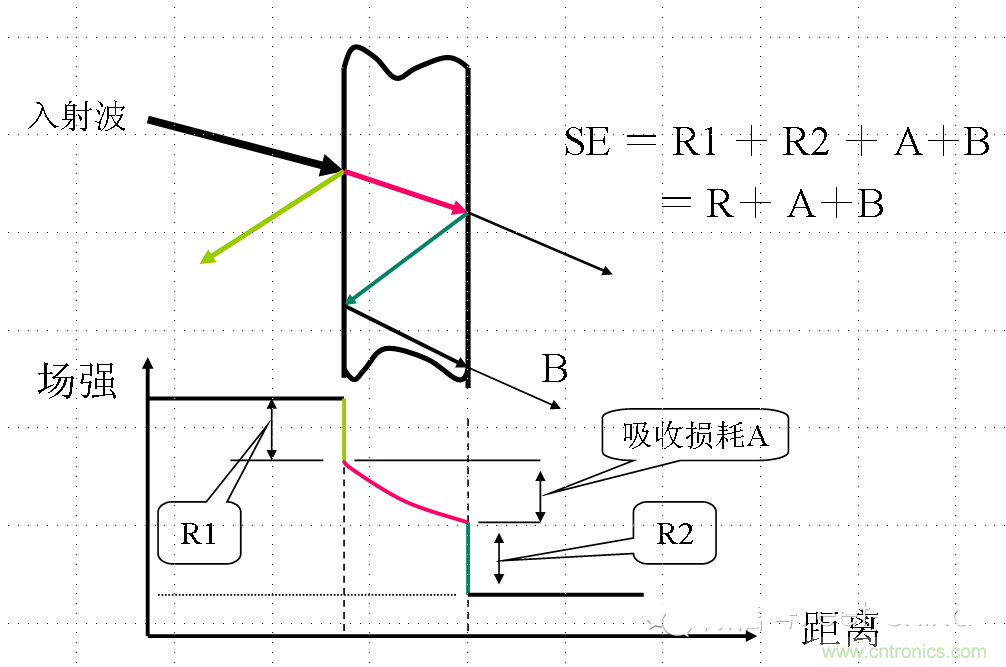

實(shí)心屏蔽把屏蔽體看成一個(gè)結(jié)構(gòu)上完整、電氣上連續(xù)均勻的無(wú)限大平板或全封閉殼體,上面不存在任何孔洞、縫隙等電氣不連續(xù)點(diǎn)。實(shí)心屏蔽理論反映了屏蔽材料在“實(shí)心”條件下所能達(dá)到的“理想屏蔽效能”,僅對(duì)屏蔽材料的研發(fā)和選用起指導(dǎo)作用。實(shí)心材料屏蔽效能的計(jì)算如圖5所示。

電磁波入射到無(wú)限大的平板型屏蔽體時(shí),一部分能量被反射,稱反射損耗,記為R1;透射波在金屬板內(nèi)傳播時(shí)被衰減,稱吸收損耗,記為A.電磁波到達(dá)屏蔽體另一側(cè)時(shí),又被反射記為R2,僅有小部分能量透射進(jìn)入被屏蔽空間。被反射的能量又被衰減和反射,循環(huán)往復(fù),直至能量全部被衰減和透射。這種多次反射的現(xiàn)象,稱多次反射修正系數(shù),記為B,量值小于1.

采用銀、銅、鋁、鎳等良導(dǎo)體制作的接地屏蔽體,可對(duì)電場(chǎng)和高頻磁場(chǎng)進(jìn)行屏蔽;當(dāng)厚度小、頻率低時(shí),鋼的屏蔽效能比銅低;當(dāng)厚度大、頻率高時(shí),鋼的屏蔽效能比銅高;當(dāng)厚度在0.67mm以上,鋼的屏蔽效能比銅高。對(duì)于近場(chǎng)電場(chǎng)屏蔽,則以銅為宜。

對(duì)于f<100kHz的低頻磁場(chǎng),則用高導(dǎo)磁材料進(jìn)行屏蔽,如工業(yè)純鐵,鐵硅合金(硅鋼,電工鋼等),鐵鎳軟磁合金,坡莫合金(79℅鎳,21℅鐵),非晶態(tài)軟磁合金材料(具有高強(qiáng)度,高硬度,高延展性,耐腐蝕性),μ金屬,鐵氧體材料等。

圖5 實(shí)心材料屏蔽效能的計(jì)算

2 屏蔽方案的級(jí)別:級(jí)別越低,越容易實(shí)現(xiàn)高屏蔽效能。

單板屏蔽及單板局部屏蔽:約20dB/1GHz

模塊屏蔽:將輻射騷擾大或抗騷擾能力差的模塊,單獨(dú)安裝在屏蔽盒中。不但容易實(shí)現(xiàn),成本低,而且可以減弱模塊之間的相互騷擾,實(shí)現(xiàn)產(chǎn)品內(nèi)部模塊之間的電磁兼容。約20dB/1GHz

插箱、子架屏蔽: 約20dB/1GHz

機(jī)柜屏蔽: 約15dB/1GHz

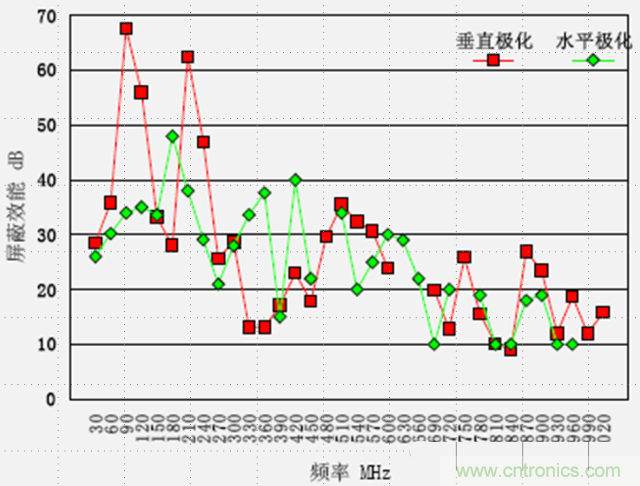

圖6為拼裝機(jī)柜的屏蔽效能,30-230MHz:20dB;230-1000MHz:10dB

圖6 拼裝機(jī)柜的屏蔽效能

二.實(shí)際屏蔽體的問題

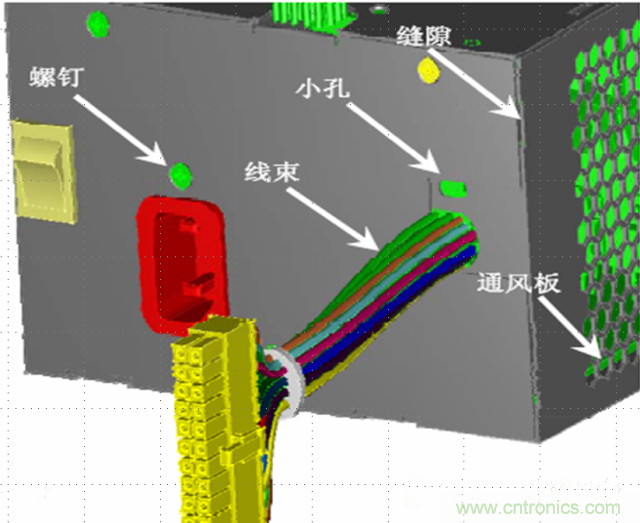

實(shí)際屏蔽體上有許多電磁泄漏源,例如:不同部分結(jié)合處的縫隙、通風(fēng)口、顯示窗、按鍵、指示燈、電纜線、電源線等,如圖7所示。

圖7 實(shí)際屏蔽體上的電磁泄漏源

1 縫隙屏蔽

:當(dāng)縫隙的長(zhǎng)度接近波長(zhǎng)的一半時(shí),電磁波就會(huì)泄漏出去。這種類型的電磁泄漏源就是狹縫天線??p隙尺寸接近半波長(zhǎng)的整數(shù)倍時(shí),電磁泄漏最大。所以,高頻時(shí)特別應(yīng)做好孔縫屏蔽,要求縫長(zhǎng)或孔徑小于l/100。整個(gè)接合處必須維持電氣連續(xù)性,以避免狹縫天線的形成。 最少要在每l/6 之處有配接表面間的電接觸-緊固點(diǎn)直接連接(包括螺釘?鉚釘點(diǎn)焊?鎖扣等)。永久性接縫,采用焊接工藝。非永久性配合面形成的接縫采用導(dǎo)電襯墊.均可達(dá)20dB/1GHz?! ?/div>

屏蔽體的導(dǎo)電連續(xù)性,是影響屏蔽效能最主要的因素。

2 通風(fēng)孔的處理

目的是處理屏蔽和散熱之間的矛盾。

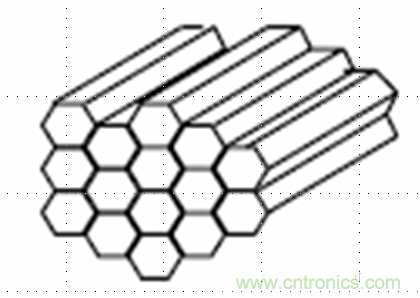

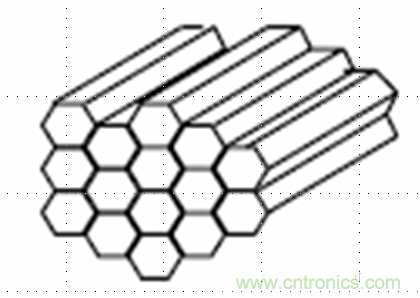

波導(dǎo)是管狀金屬結(jié)構(gòu),呈高通濾波器特性, 頻率高的電磁波能通過(guò)波導(dǎo)管,頻率低的電磁波則損耗很大。工作在截止區(qū)的波導(dǎo)管稱為截止波導(dǎo)管,可使騷擾頻率落在截止區(qū)內(nèi)而被抑制。這種裝置稱為截止波導(dǎo)通風(fēng)窗,如圖8所示,用于對(duì)屏蔽效能要求高的機(jī)柜。

圖8 截止波導(dǎo)通風(fēng)窗

截止波導(dǎo)通風(fēng)窗可抑制低于10GHz的騷擾,屏效達(dá)50-80dB/1GHz.但成本高,鋁制波導(dǎo)粘貼而成,須經(jīng)導(dǎo)電氧化,鍍錫,鍍鎳等導(dǎo)電處理,價(jià)格為1000元/m2以上.鋼制波導(dǎo)用釬焊方式制成,價(jià)格昂貴,不推薦使用.

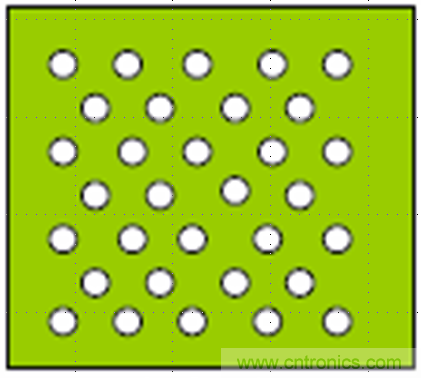

屏蔽效能要求不高的機(jī)柜,可采用金屬孔板,如圖9所示。只適用于騷擾頻率低于50MHz時(shí),屏效為30-50dB/1GHz。材料為鋼板或鋁板。

圖9 金屬孔板

3 顯示器:采用金屬鍍膜導(dǎo)電玻璃

金屬鍍膜玻璃是采用真空濺射等工藝在普通或鋼化玻璃表面形成致密導(dǎo)電膜而制成的,具有屏蔽效能高、透光率高、無(wú)光學(xué)畸變、環(huán)境適應(yīng)性強(qiáng)等優(yōu)點(diǎn)。

4 電纜或?qū)Ь€穿越屏蔽體

濾波器連接器用于多根導(dǎo)線或電纜穿越屏蔽體。穿心電容、饋通濾波器用于單根導(dǎo)線或電纜穿越屏蔽體。

5 接續(xù)設(shè)計(jì)

屏蔽層的正確接法應(yīng)采用壓接端子并360度搭接,構(gòu)成啞鈴形結(jié)構(gòu),成為屏蔽機(jī)殼的延伸。

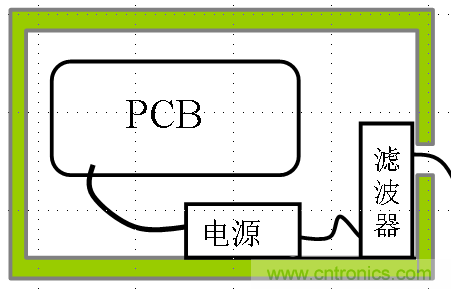

第四層 濾波設(shè)計(jì)

傳導(dǎo)騷擾可以通過(guò)電源線、信號(hào)線、互連線等導(dǎo)線,以及屏蔽體、接地導(dǎo)體等導(dǎo)體進(jìn)行傳播。解決傳導(dǎo)耦合的辦法是在騷擾進(jìn)入敏感電路之前用濾波方法從導(dǎo)線或?qū)w上除去騷擾。

電磁騷擾濾波器,即EMI濾波器,是抑制傳導(dǎo)騷擾最有效的手段。它包括信號(hào)線濾波器和電源線濾波器。信號(hào)線濾波器允許有用信號(hào)無(wú)衰減通過(guò),同時(shí)大大衰減雜波騷擾信號(hào)。電源線濾波器又稱電網(wǎng)濾波器,它以較小的衰減把直流、50Hz、400Hz電源功率傳輸?shù)皆O(shè)備上,卻大大衰減經(jīng)電源傳入的EMI信號(hào),保護(hù)設(shè)備免受其害。同時(shí),它又能抑制設(shè)備本身產(chǎn)生的EMI信號(hào),防止它進(jìn)入電網(wǎng),污染電磁環(huán)境,危害其它設(shè)備。

EMI濾波器,通常是集總參數(shù)的、無(wú)源的低通濾波器。但EMI濾波器不同于一般低通濾波器,EMI濾波器更關(guān)心插入損耗、能量衰減、截止頻率等特性。

一 影響濾波器性能的關(guān)鍵特性

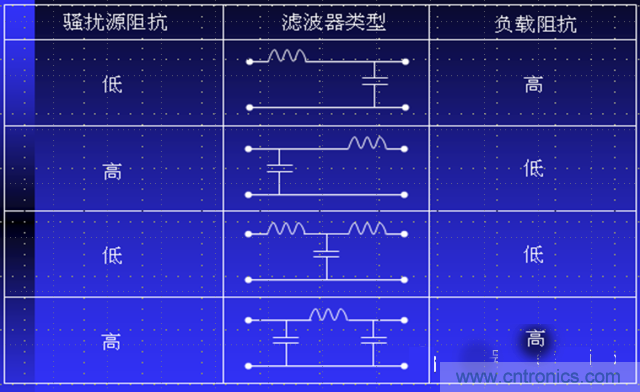

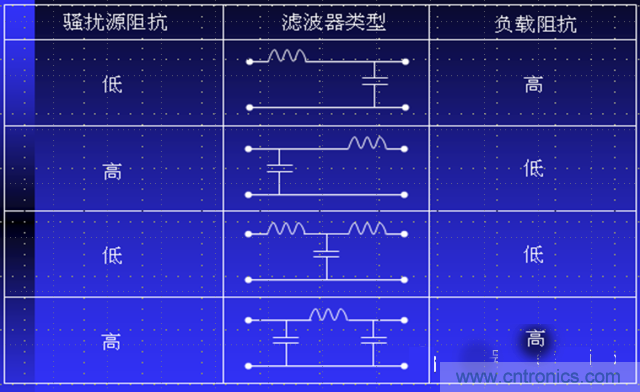

1.影響濾波器性能的關(guān)鍵特性之一:阻抗特性

無(wú)源濾波器由抑制元件組成,其抑制特性不僅取決于元件參數(shù),而且還取決于端接阻抗。 如圖10所示。

圖10 源/負(fù)載阻抗與濾波器網(wǎng)絡(luò)結(jié)構(gòu)的選擇

例如,為防止電源系統(tǒng)的不穩(wěn)定性,濾波器的輸出阻抗必須小于開關(guān)電源開環(huán)輸入阻抗。濾波器的輸入阻抗應(yīng)與電網(wǎng)輸出阻抗相差較大。其目的是為了盡可能使之失配,以獲得盡可能大的插入損耗。

2.影響濾波器性能的關(guān)鍵特性之二:頻率特性

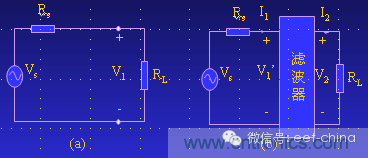

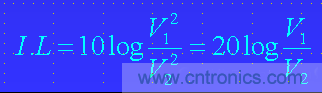

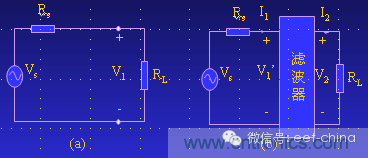

EMI濾波器的抑制噪聲能力的評(píng)定指標(biāo):插入損耗 IL(Insertion Loss)。插入損耗的定義如圖11所示。

圖11 插入損耗的定義

共模和差模插入損耗是在50~75W間的某一阻值的系統(tǒng)內(nèi)進(jìn)行測(cè)量的,是最優(yōu)化和誤導(dǎo),100/0.1Ω或0.1/100Ω系統(tǒng)才能真實(shí)地預(yù)估實(shí)際應(yīng)用時(shí)的性能。

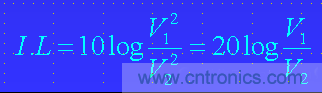

3.影響濾波器性能的關(guān)鍵特性之三:電源線濾波器的安裝

電源線濾波器安裝時(shí),容易出現(xiàn)的問題包括,濾波器輸入線過(guò)長(zhǎng)、輸入輸出發(fā)生耦合、接地不良等。針對(duì)這些問題,電源線濾波器的正確安裝應(yīng)當(dāng)如圖12所示。

圖12 電源線濾波器的正確安裝

第五層 瞬態(tài)騷擾抑制設(shè)計(jì)

一.電快速瞬變脈沖群(EFT)的抑制

抑制EFT必須做到:正確選用和安裝電源濾波器和信號(hào)濾波器:減小PCB環(huán)路面積和引線電感;分類捆扎分類敷設(shè)導(dǎo)線和電纜;控制線使用屏蔽線,電源線不應(yīng)過(guò)長(zhǎng);正確做好接地設(shè)計(jì);安裝瞬態(tài)騷擾抑制器。

二.雷擊浪涌的抑制

導(dǎo)致雷擊浪涌試驗(yàn)失敗表現(xiàn)在過(guò)高的差模電壓導(dǎo)致輸入器件被擊穿,或過(guò)高的共模電壓導(dǎo)致線路與地之間的絕緣層被擊穿。

通過(guò)雷擊浪涌敏感度試驗(yàn)應(yīng)采取的措施:浪涌吸收器件要用在進(jìn)線入口處。在器件附近不能有信號(hào)線和電源線經(jīng)過(guò),以防止將浪涌引入信號(hào)和電源線路。器件的引腳要短;吸收容量要與浪涌電壓和電流的試驗(yàn)等級(jí)相匹配。

三.靜電防護(hù)

靜電放電是高電位、強(qiáng)電場(chǎng)、瞬態(tài)大電流的過(guò)程.所產(chǎn)生的上升時(shí)間極快、持續(xù)時(shí)間極短(多數(shù)只有幾百納秒)的電磁脈沖.

1.ESD防護(hù)是一項(xiàng)系統(tǒng)工程,需要各個(gè)環(huán)節(jié)實(shí)施全面控制.一般應(yīng)達(dá)到(+/-)2000V以上的防護(hù)要求.

2.電子設(shè)備ESD保護(hù)電路設(shè)計(jì)

旁路釋放保護(hù)電路:其作用是將靜電荷通過(guò)該保護(hù)電路釋放掉,避免對(duì)功能元器件的靜電損傷;限壓/限流保護(hù)電路:其作用是減緩靜電的放電速度,使放電電壓/流小一些,鉗制器件端口的電位;采用絕緣介質(zhì)如塑料機(jī)箱、空氣間隙及絕緣材料等把內(nèi)部系統(tǒng)和元器件與外界隔離;.使用金屬屏蔽外殼,防止大的ESD電流沖擊內(nèi)部電路;.PCB板上安裝光耦合器、隔離變壓器、光纖/無(wú)線和紅外線耦合 ,實(shí)現(xiàn)電氣隔離。

四.瞬態(tài)騷擾抑制器

由于濾波器的輸入輸出阻抗與電網(wǎng)以及負(fù)載阻抗嚴(yán)重失配,對(duì)瞬態(tài)騷擾的抑制能力非常有限.目前最有效的辦法是采用瞬態(tài)騷擾抑制器,將大部分能量轉(zhuǎn)移到地。

1.避雷管:早期的避雷管是氣體放電管,一個(gè)電極接可能耦合瞬態(tài)騷擾的線路,另一個(gè)接地。瞬態(tài)騷擾出現(xiàn)時(shí),管內(nèi)氣體被電離,兩極間的電壓迅速降到很低的殘壓值(2-4kV)上,使大部份瞬態(tài)能量被地線迅速轉(zhuǎn)移,通流容量大(100kA以上),功耗大大降低,漏電流小,產(chǎn)品受到了保護(hù)。目前已固化,體積很小。避雷管具有很強(qiáng)的浪涌電流吸收能力,很高的絕緣電阻(>104MW)和很小的寄生電容(<2pF),對(duì)產(chǎn)品正常工作不會(huì)產(chǎn)生有害影響.但其響應(yīng)時(shí)間較慢,約為£100ns.只適用于線路保護(hù)和產(chǎn)品的一次保護(hù) 。

2.壓敏電阻器(VSR)(varistor; voltage-dependent resistor):為多個(gè)PN結(jié)并聯(lián)和串聯(lián)在一起的電壓敏感型箝位保護(hù)器件.當(dāng)加在其兩端的電壓低于標(biāo)稱壓敏電壓時(shí),其電阻近為無(wú)窮大,而超過(guò)標(biāo)稱壓敏電壓值后,阻值便急劇下降.它對(duì)瞬態(tài)電壓的吸收作用是通過(guò)箝位方式實(shí)現(xiàn)的,并轉(zhuǎn)換為熱量.其響應(yīng)時(shí)間<50ns.主要參數(shù)為:

1)、標(biāo)稱壓敏電壓V1mA ,即擊穿電壓或閾值電壓。指在1mA規(guī)定電流下的電壓值,即1mA直流時(shí)測(cè)得的電壓值.為10-9000V不等。一般 V1mA=1.5Vp或V1mA=2.2VAC,式中,Vp為電路額定電壓的峰值。VAC為額定交流電壓的有效值。ZnO壓敏電阻的電壓值選擇是至關(guān)重要的,它關(guān)系到保護(hù)效果與使用壽命。如額定電源電壓為220V,則壓敏電壓 V1mA=1.5Vp=1.5×1.414×220V=467V,或V1mA=2.2VAC=2.2×220V=484V.因此,選在470-480V之間。

2)、通流容量(kA) ,即在環(huán)境溫度為25℃情況下最大脈沖電流的峰值,通常選用2-20kA。

3)、 殘壓比:規(guī)定峰值為8/20ms標(biāo)準(zhǔn)沖擊電流通過(guò)壓敏電阻后, 兩端的峰值電壓值(稱為最大限制電壓)與壓敏電壓之比.約為1.7-1.8.

3.TVS(Transient Voltage Suppresser瞬態(tài)電壓抑制器)

隨著電子信息技術(shù)的迅速發(fā)展,當(dāng)前半導(dǎo)體器件日益趨向小型化、高密度和多功能化。因此要求保護(hù)器件必須具備低箝位電壓以提供有效的ESD保護(hù);而且響應(yīng)時(shí)間要快以滿足高速數(shù)據(jù)線路的要求;封裝集成度高以適用便攜設(shè)備印制電路板面緊張的情況;同時(shí)還要保證多次ESD過(guò)程后不會(huì)劣化以保證高檔設(shè)備應(yīng)有的品質(zhì)。TVS(Transient Voltage Suppresser瞬態(tài)電壓抑制器)正是為解決這些問題而產(chǎn)生的,它已成為保護(hù)電子信息設(shè)備的關(guān)鍵性技術(shù)器件,是專門設(shè)計(jì)用于吸收ESD能量并且保護(hù)系統(tǒng)免遭ESD損害的固態(tài)元件。

TVS是一種二極管形式的高效能保護(hù)器件。當(dāng)TVS二極管的兩極受到反向瞬態(tài)高能量沖擊時(shí),它能以10-12秒量級(jí)的速度,將其兩極間的高阻抗變?yōu)榈妥杩?,吸收高達(dá)數(shù)千瓦的浪涌功率,使兩極間的電壓箝位于一個(gè)預(yù)定值,有效地保護(hù)電子線路中的精密元器件,免受各種浪涌脈沖的損壞。由于它具有響應(yīng)時(shí)間快、瞬態(tài)功率大、漏電流低、擊穿電壓偏差小、箝位電壓較易控制、無(wú)損壞極限、體積小等優(yōu)點(diǎn)。

目前已廣泛應(yīng)用于計(jì)算機(jī)系統(tǒng)、通訊設(shè)備、交/直流電源、汽車、電子鎮(zhèn)流器、家用電器、儀器儀表(電度表)、RS232/422/423/485、I/O、LAN、ISDN、ADSL、USB、MP3、PDAS、GPS、CDMA、GSM、數(shù)字照相機(jī)的保護(hù)、共模/差模保護(hù)、RF耦合/IC驅(qū)動(dòng)接收保護(hù)、電機(jī)電磁騷擾抑制、聲頻/視頻輸入、傳感器/變速器、工控回路、繼電器、接觸器噪音的抑制等各個(gè)領(lǐng)域。

第六層 系統(tǒng)級(jí)電磁兼容設(shè)計(jì)

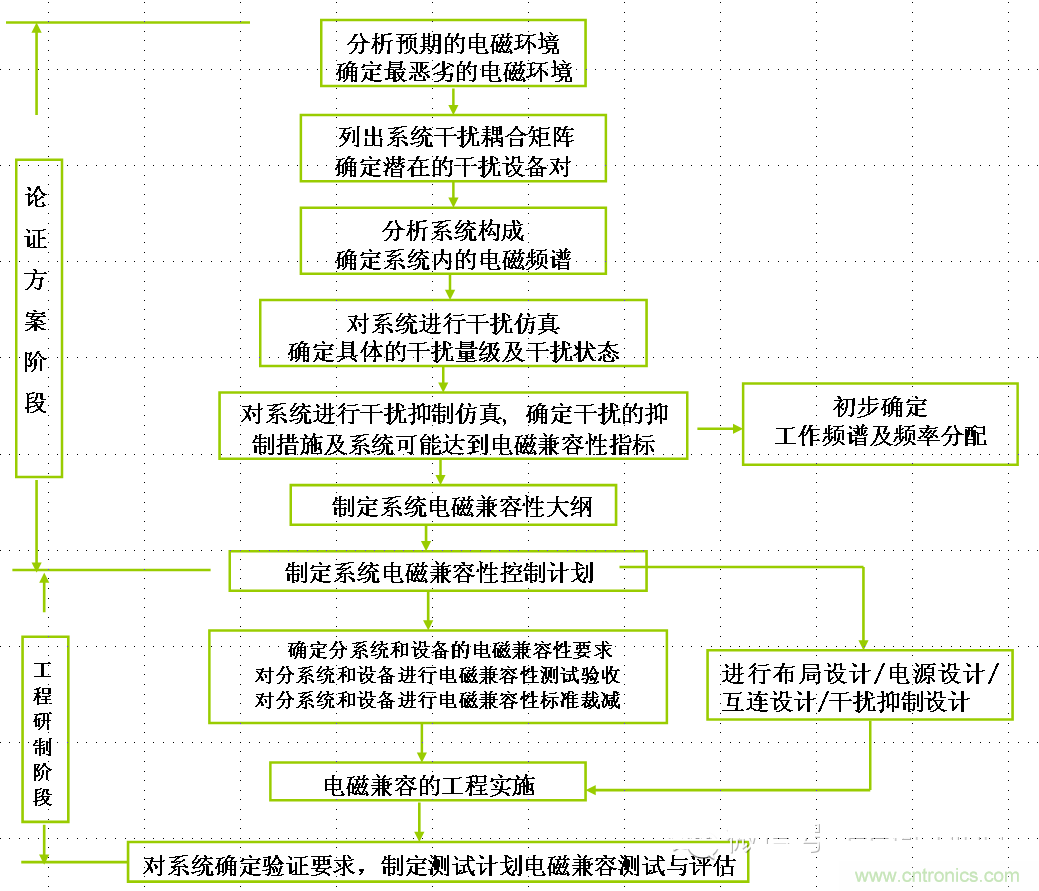

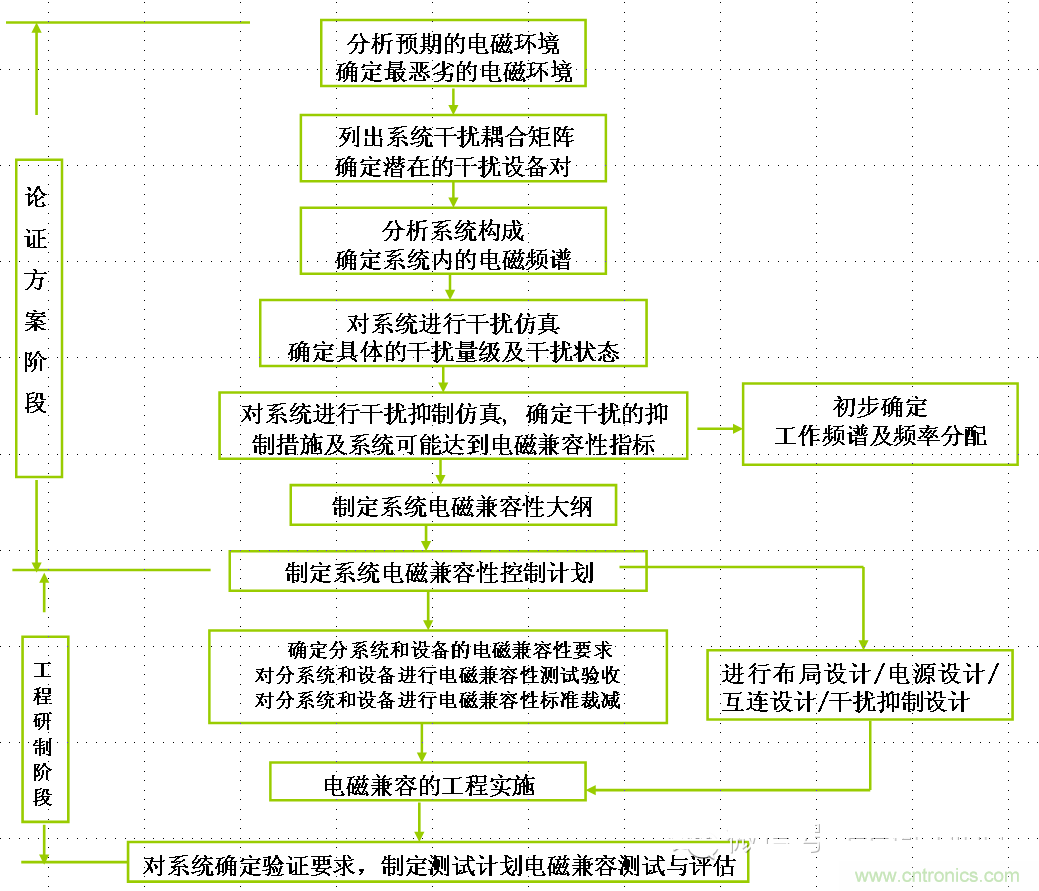

EMC對(duì)系統(tǒng)效能的影響包括:系統(tǒng)性能降低或失效;系統(tǒng)可靠性降低;影響系統(tǒng)工作壽命;影響效/費(fèi)比的權(quán)衡;影響系統(tǒng)和人員的生存性和安全性;延誤生產(chǎn)和使用。系統(tǒng)級(jí)電磁兼容設(shè)計(jì)流程如圖13所示。

圖13 系統(tǒng)級(jí)電磁兼容設(shè)計(jì)流程

實(shí)踐表明,滿足了設(shè)備EMC限值的設(shè)備、分系統(tǒng)組成系統(tǒng)后并不能保證系統(tǒng)的EMC良好,即EMC+EMC¹EMC。因此規(guī)定系統(tǒng)的EMC要求并實(shí)現(xiàn)它是與保證設(shè)備EMC同等重要的。例如,如果N個(gè)模塊分別在場(chǎng)點(diǎn)測(cè)得的場(chǎng)強(qiáng)值基本相等,則

Eo=N1/2E(mV/m)

設(shè)標(biāo)準(zhǔn)規(guī)定的騷擾發(fā)射限值為Eo,若有N個(gè)模塊,則每個(gè)模塊的騷擾發(fā)射限值應(yīng)為

E=Eo/N1/2

十余年來(lái),“電磁兼容分層與綜合設(shè)計(jì)法”已成功用于,合成孔徑雷達(dá)衛(wèi)星、大型集裝箱檢查系統(tǒng)、手持機(jī)、集成電路、汽車電子系統(tǒng)、醫(yī)用電子設(shè)備與系統(tǒng)、嵌入式機(jī)器人控制器等的電磁兼容設(shè)計(jì),基本做到電磁兼容試驗(yàn)一次成功。

以上內(nèi)容轉(zhuǎn)載自電子工程專輯。

推薦閱讀: