【導(dǎo)讀】本文將描述在SoC設(shè)計(jì)方法論中追求新流程的目的。該流程包括提取、評(píng)估和分析復(fù)雜SoC及其封裝環(huán)境的全電磁耦合模型。分析結(jié)果強(qiáng)調(diào)了電磁耦合對(duì)現(xiàn)代復(fù)雜SOC設(shè)計(jì)性能和功能的影響。

本文將描述在SoC設(shè)計(jì)方法論中追求新流程的目的。該流程包括提取、評(píng)估和分析復(fù)雜SoC及其封裝環(huán)境的全電磁耦合模型。分析結(jié)果強(qiáng)調(diào)了電磁耦合對(duì)現(xiàn)代復(fù)雜SOC設(shè)計(jì)性能和功能的影響。

背景

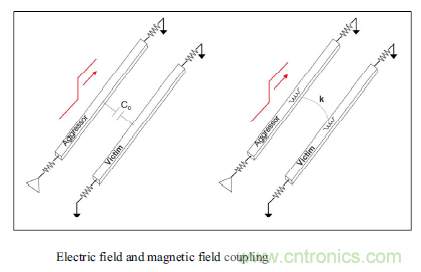

隨著納米尺度技術(shù)的引入,互連線的縱橫展弦比提高了。因此,來自鄰近攻擊者的電容串?dāng)_對(duì)受害者網(wǎng)絡(luò)會(huì)有這更大的影響,這就需要新改進(jìn)的SoC設(shè)計(jì)流。為確保從攻擊者處注入(靜止)受害者網(wǎng)絡(luò)的(累積)能量不會(huì)導(dǎo)致電路網(wǎng)絡(luò)故障,我們就需要全新的噪聲分析工具和相應(yīng)的IP表征方法。在靜態(tài)時(shí)序分析流中用于互連延遲計(jì)算的算法得到了擴(kuò)展,它反映了噪聲對(duì)延遲的影響,這是由于過渡信號(hào)在攻擊器上的并發(fā)轉(zhuǎn)換在輸出端可能產(chǎn)生的波形變化造成的。

用于物理實(shí)現(xiàn)的EDA工具也包含了新的特性。詳細(xì)的路由算法得到了擴(kuò)展,包括對(duì)相鄰互連的并行運(yùn)行長度的限制。同時(shí),采用了更復(fù)雜的噪聲計(jì)算/避免方法來輔助布線軌道的選擇。

設(shè)計(jì)人員采用的技術(shù)以進(jìn)一步降低隨后電容串?dāng)_噪聲失效的風(fēng)險(xiǎn)。此外,對(duì)關(guān)鍵網(wǎng)的特定非默認(rèn)繞線規(guī)則(NDR)進(jìn)行了編碼,以指導(dǎo)實(shí)現(xiàn)工具在層上的金屬段之間使用大于最小的間距,或?qū)⒍我龑?dǎo)到與非開關(guān)(電源/接地)網(wǎng)絡(luò)相鄰的軌道,以有效地屏蔽節(jié)段與耦合轉(zhuǎn)換。

金屬節(jié)段之間的電容電場(chǎng)線的有限范圍相對(duì)容易地結(jié)合到SoC物理設(shè)計(jì)和電分析流中,由庫單元輸出驅(qū)動(dòng)器波形和輸入管腳噪聲靈敏度模型(標(biāo)準(zhǔn))支持。

隨著SoC時(shí)鐘頻率目標(biāo)的增加和納米設(shè)計(jì)中電源電壓的縮放,特定網(wǎng)的(自)電感的影響變得更加明顯。通過將提取的RLC模型應(yīng)用于P/G柵格,將開關(guān)電流源注入到柵格位置,對(duì)其進(jìn)行功率/地噪聲裕度分析。此外,我們利用電感元件分析時(shí)鐘網(wǎng)的轉(zhuǎn)換速率,對(duì)時(shí)鐘驅(qū)動(dòng)器轉(zhuǎn)換的(諧波)高頻內(nèi)容呈現(xiàn)附加阻抗。

參考文獻(xiàn)的案例描述了一種有代表性的金屬節(jié)段集合的偏電感提取方法——假設(shè)部分電感用于一個(gè)節(jié)段,以減輕定義“全回路”電流返回路徑的困難。但時(shí)鐘信號(hào)分布可能會(huì)受到影響。

當(dāng)今SoC設(shè)計(jì)的電磁建模要求

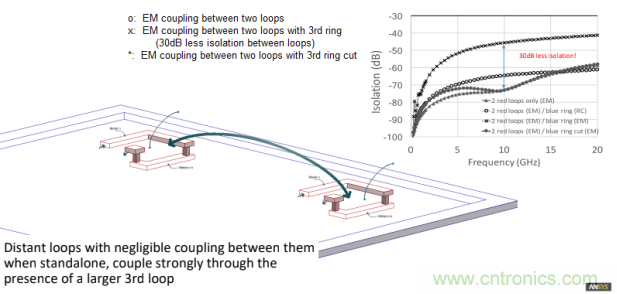

現(xiàn)代SoC設(shè)計(jì)的復(fù)雜性集成了一組極為多樣化的高性能IP,并相應(yīng)地增加了不同物理塊之間電磁耦合的潛力。為了表示芯片上電流環(huán)之間的互感遠(yuǎn)距離相互作用,我們將P/G柵極和時(shí)鐘網(wǎng)的隔離(部分)電感模型進(jìn)行擴(kuò)展。

上圖說明了對(duì)這種物理耦合建模的重要性。設(shè)計(jì)中兩個(gè)“隔離”的小環(huán)路相距1mm,當(dāng)完全提取并一起分析時(shí),它們是孤立的,耦合非常弱。設(shè)計(jì)還包括第三個(gè)更大的20毫米x 25毫米的環(huán)。當(dāng)考慮第三大環(huán)的RC效應(yīng)時(shí),對(duì)兩個(gè)線圈之間的隔離影響會(huì)很小。然而,在進(jìn)行全電磁(EM)提取(RLCk)和分析時(shí),從圖中可以看出,由于額外的EM耦合,兩個(gè)小環(huán)路之間的隔離在10GHz時(shí)降低了30dB。注意,第三環(huán)/環(huán)路在物理上并不與兩個(gè)IP環(huán)路相鄰——全電磁耦合不同于短距離的電場(chǎng)電容性串?dāng)_。

(附帶說明,為了證明EM耦合來自于第三個(gè)循環(huán),對(duì)第3個(gè)循環(huán)“cut”做了額外的分析——隔離返回到2個(gè)循環(huán)的結(jié)果,如上圖所示。)

有助于電磁耦合的芯片上的周圍結(jié)構(gòu)包括多種可能性,例如P/G柵極(帶有去耦蓋)、密封環(huán)、大塊硅襯底、封裝上的重分布層金屬等。

那么,為什么會(huì)出現(xiàn)SoC EM耦合問題呢?

上圖說明了IP塊之間的隔離主要是在非常高的頻率上受到影響??紤]一下當(dāng)前SoC的設(shè)計(jì),其中許多串行收發(fā)信路被封裝在芯片上——例如,這些SerDes通道可以在7GHz下傳輸PAM-4 56Gbps的信號(hào)。一組通道將共享一個(gè)公共VCO/PLL時(shí)鐘源——多個(gè)組將被集成以提供所需的總數(shù)據(jù)帶寬。(每個(gè)組也可以有多個(gè)內(nèi)部的VCO,以跨越更大的發(fā)射頻率范圍。) 在多個(gè)SerDes通道、它們的P/G網(wǎng)絡(luò)、密封環(huán)和封裝結(jié)構(gòu)之間的磁力耦合可能會(huì)導(dǎo)致時(shí)鐘抖動(dòng)顯著增加,從而導(dǎo)致不可接受的誤碼率。

如前所述,當(dāng)今高級(jí)封裝的拓?fù)涫荅M耦合模型的關(guān)鍵部分。它需要包含2.5D封裝(含插接器)中的再分配和功率傳遞金屬。在3D封裝中,多個(gè)堆疊、變薄的模具的獨(dú)特特性也需要EM耦合模型。

EM耦合工具

這就需要SoC團(tuán)隊(duì)將EM耦合分析添加到簽名方法中(sign-off),這就需要新的工具/流程來幫助設(shè)計(jì)人員完成EM模型提取和仿真的艱巨任務(wù)。

最近,我有機(jī)會(huì)與ANSYS的工程副總裁Yorgos Koutsoyannopoulos討論了最新的電磁耦合工具/流的進(jìn)展。

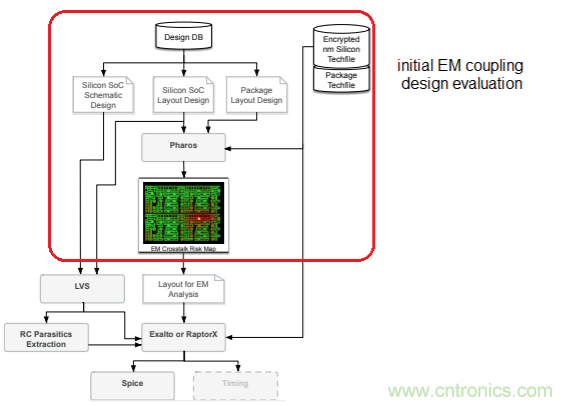

Yorgos表示:“我們將電磁耦合分析任務(wù)分為兩部分。最終目標(biāo)是為設(shè)計(jì)師提供設(shè)計(jì)中所有相關(guān)結(jié)構(gòu)的RLCk模型,并對(duì)電路級(jí)模型進(jìn)行時(shí)間、頻率、噪聲的模擬。”然而,整個(gè)芯片封裝的數(shù)據(jù)量將是不可管理的,并且SoC上的大部分IP信號(hào)將不會(huì)時(shí)候到關(guān)注。我們開發(fā)了一個(gè)評(píng)估流程,以幫助設(shè)計(jì)師確定具體的網(wǎng)絡(luò),在那里可進(jìn)行詳細(xì)的電磁耦合模型仿真。”

“完整的芯片封裝模型最初生成的評(píng)價(jià)是?”

Yorgos解釋:“使用ANSYS Pharos工具評(píng)估流程的重點(diǎn)是評(píng)估SoC金屬、vias、電介質(zhì)和襯底模型,而不是考慮電路級(jí)的細(xì)節(jié)。設(shè)計(jì)者感興趣的(頂級(jí))互連層,并構(gòu)造拓?fù)淠P褪窃谖锢頂帱c(diǎn)處自動(dòng)添加端口。在這個(gè)連接處,如果沒有底層電路,就沒有提取出的RLCk模型的標(biāo)注——芯片就不需要LVS低速掃描。為了檢測(cè)更大的循環(huán),分析將跨越SoC IP物理層次結(jié)構(gòu)。我們的目標(biāo)是找到相互作用的結(jié)構(gòu),以保證進(jìn)一步的、詳細(xì)的模擬。”

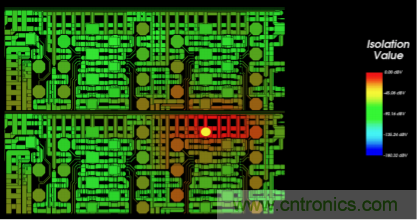

“會(huì)給設(shè)計(jì)師什么反饋?”

Yorgos:“ANSYS Pharos為相關(guān)的視覺反饋提供了切除布局?jǐn)?shù)據(jù)庫上的兩種通用熱圖,并為后續(xù)的模擬選擇了網(wǎng)格。被切除的模型按照設(shè)計(jì)師提供的頻率范圍(和增量)再進(jìn)行評(píng)估。”

“即使是切除SoC模型,這仍然是一個(gè)龐大的物理數(shù)據(jù)量-什么樣的IT資源需要這種的早期評(píng)估?”

例如,對(duì)于選擇頂部5個(gè)金屬層的100mm**2晶圓,在64核1TB內(nèi)存占用服務(wù)器上,每個(gè)頻率點(diǎn)的熱圖大約需要1-3個(gè)小時(shí)。”,Yorgos回答。(還不錯(cuò),我想。)

Yorgos:“Pharos使用與其他流程相同的互連技術(shù),包括將金屬薄片電阻率作為線寬的函數(shù)和工藝角的定義。對(duì)于帶有封裝模型的晶圓,我們能夠?qū)⒎庋b堆棧定義和重分發(fā)層包含到一個(gè)統(tǒng)一的提取模型中。我們也有一個(gè)先進(jìn)的方法,將模具基板建模成一個(gè)非常精確的鋼筋混凝土網(wǎng)格網(wǎng)絡(luò)。”

就像擴(kuò)展設(shè)計(jì)方法以支持電容性串?dāng)_的影響一樣,高性能SoC IP(可能使用高級(jí)封裝)將越來越需要采用廣泛的電磁耦合分析方法。

參考文獻(xiàn):

[1] Ruehli, A.E., “Inductance Calculations in a Complex IC Environment”, IBM Journal of Research and Development, p. 470-481, September 1972.

[2] White, et al., “FASTHENRY: A Multipole-Acclerated 3D Inductance Extraction Algorithm”, IEEE Transactions on Microwave Theory and Techniques, Vol. 42, No. 9, p. 1750-1758, September, 1994.

[3] Restle, P., and Deutsch, A., “Designing the best clock distribution network”, VLSI Circuits Symposium, p. 2-5, 1998.

[4] Raman, A., et al., “Electromagnetic Crosstalk Failures and Symptoms in SoC Designs”, 2017 18th International Workshop on Microprocessor and SoC Test and Verification, p. 39-43.

[5] Papadopoulos, P., et al., “Challenges and Trends in SoC Electromagnetic Crosstalk”, 2017 2nd International Verification and Security Workshop (IVSW), p. 63-69.

技術(shù)名詞解釋:

NDR

全稱是 Non default routing rule, 非默認(rèn)繞線規(guī)則。一般用于設(shè)置 clock 時(shí)鐘走線的規(guī)則。時(shí)鐘的翻轉(zhuǎn)頻率較高,clock path 上受到的串?dāng)_以及 EM 影響也較大。因此,通常會(huì)采取雙倍寬度的繞線寬度。默認(rèn)的繞線規(guī)則都是單位寬度,就是指 technology lef 中定義的金屬層寬度。如果我們需要采取雙倍寬度的繞線規(guī)則,那我們就需要先定義 NDR,然后工具才能使用這個(gè)規(guī)則。對(duì)于 NDR,我們可以定義在 LEF 中,也可以直接用命令定義。

電磁耦合

電磁耦合又稱互感耦合,它是由于兩個(gè)電路之間存在互感,使一個(gè)電路的電流變化通過互感影響到另一個(gè)電路。兩個(gè)或兩個(gè)以上的電路元件或電網(wǎng)絡(luò)的輸入與輸出之間存在緊密配合與相互影響,并通過相互作用從一側(cè)向另一側(cè)傳輸能量的現(xiàn)象;概括的說耦合就是指兩個(gè)實(shí)體相互依賴于對(duì)方的一個(gè)量度。

(來源:Semiwiki,Tom Dillinger)