【導(dǎo)讀】成功的RF設(shè)計(jì)必須仔細(xì)注意整個(gè)設(shè)計(jì)過程中每個(gè)步驟及每個(gè)細(xì)節(jié),這意味著必須在設(shè)計(jì)開始階段就要進(jìn)行徹底的、仔細(xì)的規(guī)劃,并對(duì)每個(gè)設(shè)計(jì)步驟的進(jìn)展進(jìn)行全面持續(xù)的評(píng)估。而這種細(xì)致的設(shè)計(jì)技巧正是國(guó)內(nèi)大多數(shù)電子企業(yè)文化所欠缺的。

1、射頻電路中元器件封裝的注意事項(xiàng)

成功的RF設(shè)計(jì)必須仔細(xì)注意整個(gè)設(shè)計(jì)過程中每個(gè)步驟及每個(gè)細(xì)節(jié),這意味著必須在設(shè)計(jì)開始階段就要進(jìn)行徹底的、仔細(xì)的規(guī)劃,并對(duì)每個(gè)設(shè)計(jì)步驟的進(jìn)展進(jìn)行全面持續(xù)的評(píng)估。而這種細(xì)致的設(shè)計(jì)技巧正是國(guó)內(nèi)大多數(shù)電子企業(yè)文化所欠缺的。

近幾年來,由于藍(lán)牙設(shè)備、無線局域網(wǎng)絡(luò)(WLAN)設(shè)備,和移動(dòng)電話的需求與成長(zhǎng),促使業(yè)者越來越關(guān)注RF電路設(shè)計(jì)的技巧。從過去到現(xiàn)在,RF電路板設(shè)計(jì)如同電磁干擾(EMI)問題一樣,一直是工程師們最難掌控的部份,甚至是夢(mèng)魘。若想要一次就設(shè)計(jì)成功,必須事先仔細(xì)規(guī)劃和注重細(xì)節(jié)才能奏效。

射頻(RF)電路板設(shè)計(jì)由于在理論上還有很多不確定性,因此常被形容為一種「黑色藝術(shù)」(black art) 。但這只是一種以偏蓋全的觀點(diǎn),RF電路板設(shè)計(jì)還是有許多可以遵循的法則。不過,在實(shí)際設(shè)計(jì)時(shí),真正實(shí)用的技巧是當(dāng)這些法則因各種限制而無法實(shí)施時(shí),如何對(duì)它們進(jìn)行折衷處理。重要的RF設(shè)計(jì)課題包括:阻抗和阻抗匹配、絕緣層材料和層疊板、波長(zhǎng)和諧波...等。

在 WiFi 產(chǎn)品的開發(fā)過程中,射頻電路的布線(RF Circuit Layout Guide)是極為關(guān)鍵的一個(gè)過程。很多時(shí)候,我們可能在原理上已經(jīng)設(shè)計(jì)的很完善,但是在實(shí)際的制板,上件過后發(fā)現(xiàn)很不理想,實(shí)際上這些都是布線(Layout)做的不夠完善的原因。本文將以一個(gè)無線網(wǎng)卡的布線實(shí)例及本人的一點(diǎn)工作經(jīng)驗(yàn)為大家講解一下射頻電路在布線中應(yīng)該注意的一些問題。

電路板的疊構(gòu)(PCB Stack Up)

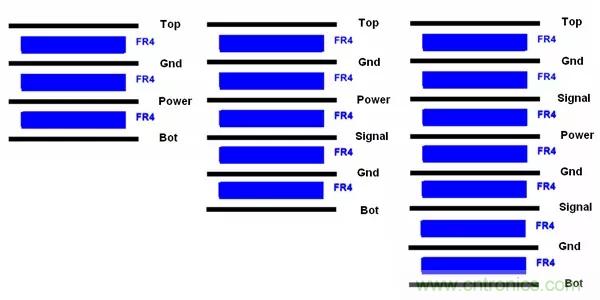

在進(jìn)行布線之前,我們首先要確定電路板的疊構(gòu),就像蓋房子要先有房子的墻壁。電路板的疊構(gòu)的確定與電路設(shè)計(jì)的復(fù)雜度,電磁兼容的考慮等很多因素有關(guān)。下圖給出了四層板,六層板和八層板的常用疊構(gòu)方式。

在無線網(wǎng)卡的PCB疊構(gòu)中,基本上不會(huì)出現(xiàn)單面板的情況,所以本文也不會(huì)對(duì)單面板的情況加以討論。兩層板設(shè)計(jì)中應(yīng)該注意的問題。

在四層板的設(shè)計(jì)中,我們一般會(huì)將第二層作為完整的地平面,同時(shí),也會(huì)把重要的信號(hào)線走在頂層(當(dāng)然包括射頻走線),以便于很好的控制阻抗。在六層板或者更多層板的設(shè)計(jì)中,我們同樣會(huì)將第二層作為完整的地平面,然后在頂層走最重要的信號(hào)線。

PS:可以使用Polar計(jì)算單端阻抗與阻抗等,有些Layout軟件自身就集成了阻抗計(jì)算器,如Allegro。

阻抗控制

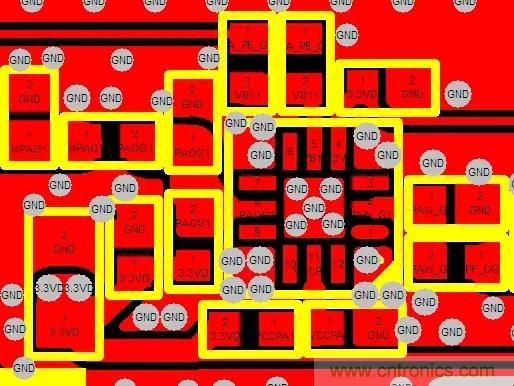

在我們進(jìn)行原理設(shè)計(jì)與仿真之后,在Layout中很值得注意的一件事情就是阻抗控制。眾所周知,我們應(yīng)該盡量保證走線的特征是50歐姆,這主要和線寬有關(guān),在本實(shí)例中,是兩層半,在Polar中采用Surface Coplanar Line模型進(jìn)行阻抗的計(jì)算,我們可以得到一組比較理想的值:Height(H)=39.6mil,Track(W)=30mil,Track(W1)=30mil,Thickness=1OZ=1.4mil, Separation(S)=7mil, Dielectric(Er)=4.2,對(duì)應(yīng)的特征阻抗是52.14歐姆,符合要求。如下圖中高亮的線就是這樣的一條射頻走線。

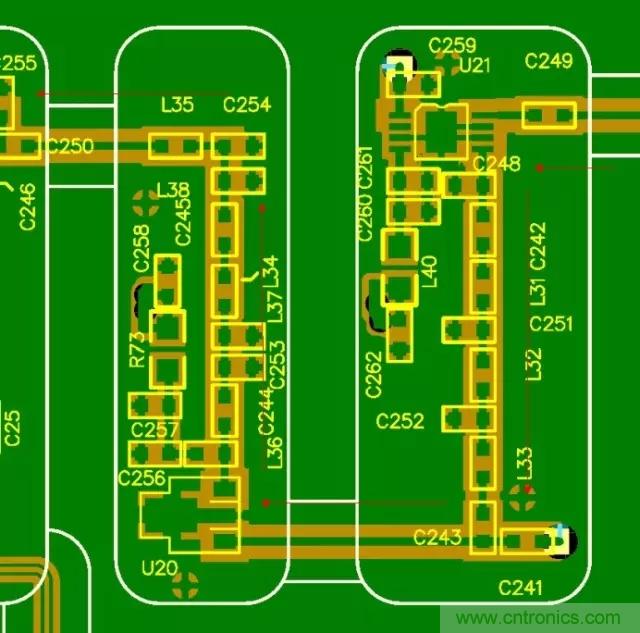

射頻元器件的擺放

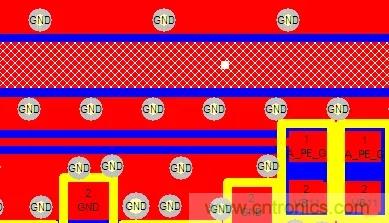

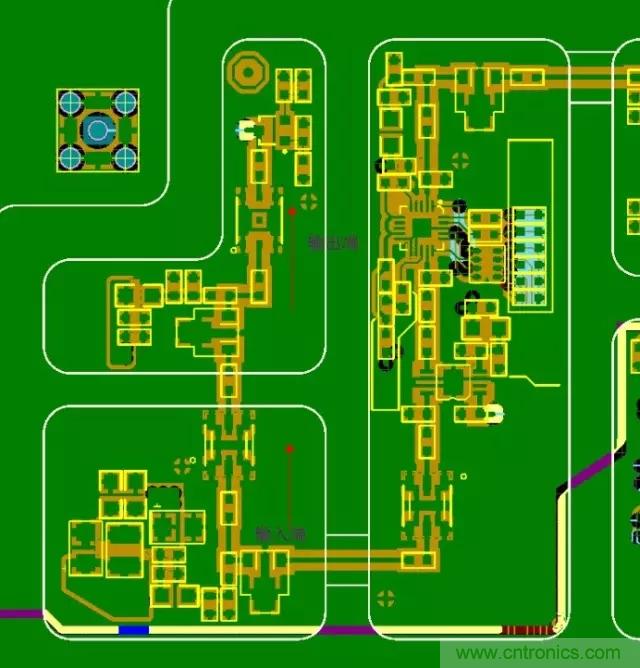

相信做過射頻設(shè)計(jì)的人都應(yīng)該知道,我們應(yīng)該盡可能的使走線的長(zhǎng)度較短,元器件擺放的越緊湊越好(特殊要求除外),同時(shí),也會(huì)盡可能的保證元器件的擺放對(duì)布線很有利(不要使走線繞來繞去的)。如下圖,是射頻功率放大器(PA,Power Amplifier)的周圍器件的擺放,我們看到,元器件之間的距離很小。

射頻走線應(yīng)該注意的問題

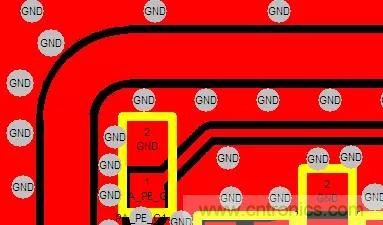

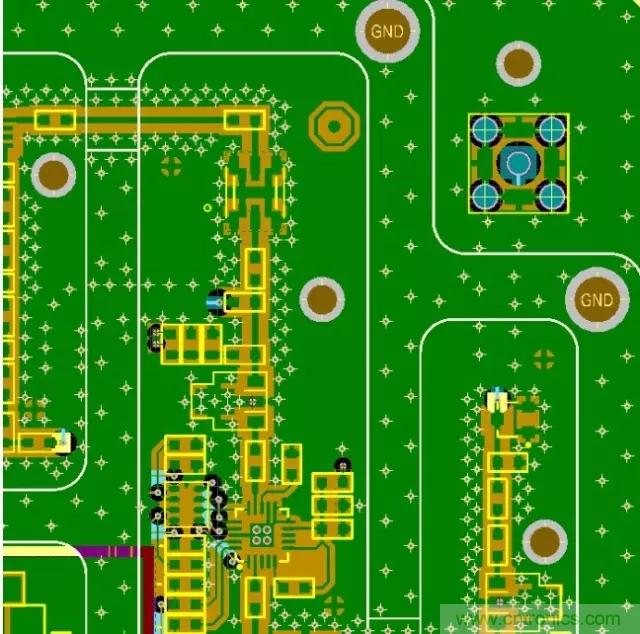

如前所述,射頻走線的長(zhǎng)度要盡量短,線寬嚴(yán)格按照計(jì)算好的值去設(shè)定。在走線是尤其要注意的是,射頻走線中不要有任何帶有尖狀的折點(diǎn),在走線的轉(zhuǎn)折處,最好要用弧線來實(shí)現(xiàn),如下圖

其次,在多層板的走線中,有可能重要的射頻線要產(chǎn)生不可避免的交叉,這時(shí)我們就要使用我們最不想使用的東西:過孔。這樣,會(huì)有部分射頻信號(hào)線走到底層甚至中間層,但無論是哪一層,射頻走線一定會(huì)有參考平面,這時(shí)一個(gè)值得注意的問題就是不要跨層,或者說不要使地平面不連續(xù)。

過孔的放置

過孔的放置真的是一件比較復(fù)雜的事情,本文只討論那種接地的過孔。

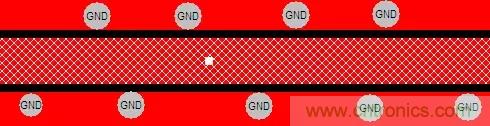

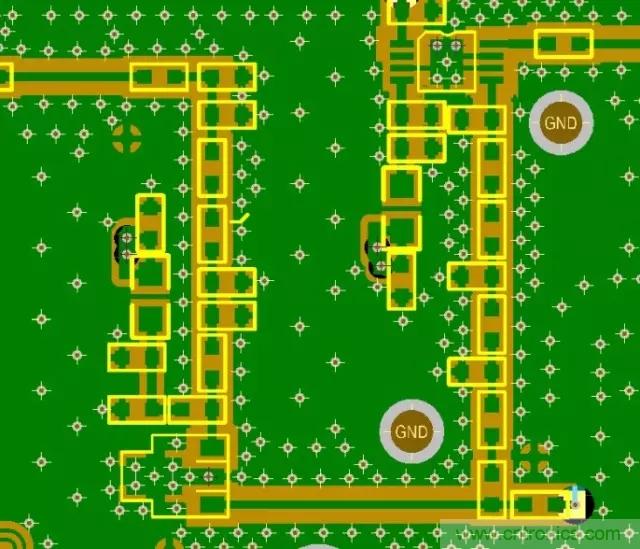

首先,射頻走線的旁邊的地線最好能通過過孔打穿,接到底層或者中間層的地平面上,這樣可以是任何干擾信號(hào)或者輻射有最短的到地的通路,但是,過孔與射頻信號(hào)線的距離又不能太近,否則會(huì)嚴(yán)重影響射頻信號(hào)質(zhì)量,在實(shí)際的設(shè)計(jì)過程中可靈活把握,如下圖,我們看到,高亮的信號(hào)線兩層分布著很多過孔。

其次,在面積較大的地平面處,我們通常會(huì)放置很多的過孔用于連接不同層的地。這在射頻電路的布線中,要注意的就是大過孔要沒有規(guī)律的打,最好能弄成菱形的,這樣可以最大限度的抑制各種干擾。

2、射頻電路電源設(shè)計(jì)注意事項(xiàng)

(1)電源線是EMI 出入電路的重要途徑。通過電源線,外界的干擾可以傳入內(nèi)部電路,影響RF電路指標(biāo)。為了減少電磁輻射和耦合,要求DC-DC模塊的一次側(cè)、二次側(cè)、負(fù)載側(cè)環(huán)路面積最小。電源電路不管形式有多復(fù)雜,其大電流環(huán)路都要盡可能小。電源線和地線總是要很近放置。

(2)如果電路中使用了開關(guān)電源,開關(guān)電源的外圍器件布局要符合各功率回流路徑最短的原則。濾波電容要靠近開關(guān)電源相關(guān)引腳。使用共模電感,靠近開關(guān)電源模塊。

(3)單板上長(zhǎng)距離的電源線不能同時(shí)接近或穿過級(jí)聯(lián)放大器(增益大于45dB)的輸出和輸入端附近。避免電源線成為RF信號(hào)傳輸途徑,可能引起自激或降低扇區(qū)隔離度。長(zhǎng)距離電源線的兩端都需要加上高頻濾波電容,甚至中間也加高頻濾波電容。

(4)RF PCB的電源入口處組合并聯(lián)三個(gè)濾波電容,利用這三種電容的各自優(yōu)點(diǎn)分別濾除電源線上的低、中、高頻。例如:10uf,0.1uf,100pf。并且按照從大到小的順序依次靠近電源的輸入管腳。

(5)用同一組電源給小信號(hào)級(jí)聯(lián)放大器饋電,應(yīng)當(dāng)先從末級(jí)開始,依次向前級(jí)供電,使末級(jí)電路產(chǎn)生的EMI 對(duì)前級(jí)的影響較小。且每一級(jí)的電源濾波至少有兩個(gè)電容:0.1uf,100pf。當(dāng)信號(hào)頻率高于1GHz時(shí),要增加10pf濾波電容。

(6)常用到小功率電子濾波器,濾波電容要靠近三極管管腳,高頻濾波電容更靠近管腳。三極管選用截止頻率較低的。如果電子濾波器中的三極管是高頻管,工作在放大區(qū),外圍器件布局又不合理,在電源輸出端很容易產(chǎn)生高頻振蕩。線性穩(wěn)壓模塊也可能存在同樣的問題,原因是芯片內(nèi)存在反饋回路,且內(nèi)部三極管工作在放大區(qū)。在布局時(shí)要求高頻濾波電容靠近管腳,減小分布電感,破壞振蕩條件。

(7)PCB的POWER部分的銅箔尺寸符合其流過的最大電流,并考慮余量(一般參考為1A/mm線寬)。

(8)電源線的輸入輸出不能交叉。

(9)注意電源退耦、濾波,防止不同單元通過電源線產(chǎn)生干擾,電源布線時(shí)電源線之間應(yīng)相互隔離。電源線與其它強(qiáng)干擾線(如CLK)用地線隔離。

(10)小信號(hào)放大器的電源布線需要地銅皮及接地過孔隔離,避免其它EMI干擾竄入,進(jìn)而惡化本級(jí)信號(hào)質(zhì)量。

(11)不同電源層在空間上要避免重疊。主要是為了減少不同電源之間的干擾,特別是一些電壓相差很大的電源之間,電源平面的重疊問題一定要設(shè)法避免,難以避免時(shí)可考慮中間隔地層。

(12)PCB板層分配便于簡(jiǎn)化后續(xù)的布線處理,對(duì)于一個(gè)四層PCB板(WLAN中常用的電路板),在大多數(shù)應(yīng)用中用電路板的頂層放置元器件和RF引線,第二層作為系統(tǒng)地,電源部分放置在第三層,任何信號(hào)線都可以分布在第四層。

第二層采用連續(xù)的地平面布局對(duì)于建立阻抗受控的RF信號(hào)通路非常必要,它還便于獲得盡可能短的地環(huán)路,為第一層和第三層提供高度的電氣隔離,使得兩層之間的耦合最小。當(dāng)然,也可以采用其它板層定義的方式(特別是在電路板具有不同的層數(shù)時(shí)),但上述結(jié)構(gòu)是經(jīng)過驗(yàn)證的一個(gè)成功范例。

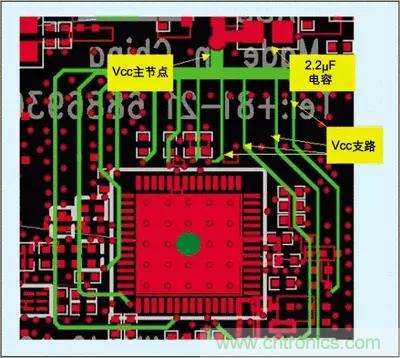

(13)大面積的電源層能夠使Vcc布線變得輕松,但是,這種結(jié)構(gòu)常常是引發(fā)系統(tǒng)性能惡化的導(dǎo)火索,在一個(gè)較大平面上把所有電源引線接在一起將無法避免引腳之間的噪聲傳輸。反之,如果使用星型拓?fù)鋭t會(huì)減輕不同電源引腳之間的耦合。

上圖給出了星型連接的Vcc布線方案,該圖取自MAX2826 IEEE 802.11a/g收發(fā)器的評(píng)估板。圖中建立了一個(gè)主Vcc節(jié)點(diǎn),從該點(diǎn)引出不同分支的電源線,為RF IC的電源引腳供電。每個(gè)電源引腳使用獨(dú)立的引線在引腳之間提供了空間上的隔離,有利于減小它們之間的耦合。另外,每條引線還具有一定的寄生電感,這恰好是我們所希望的,它有助于濾除電源線上的高頻噪聲。

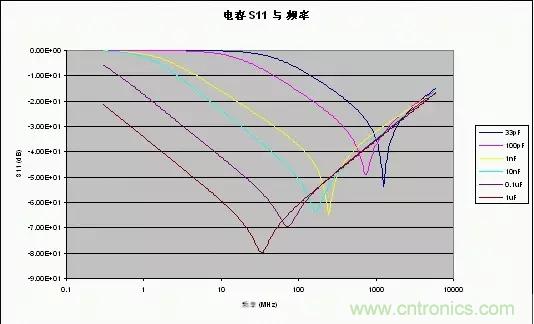

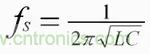

使用星型拓?fù)銿cc引線時(shí),還有必要采取適當(dāng)?shù)碾娫慈ヱ?,而去耦電容存在一定的寄生電感。事?shí)上,電容等效為一個(gè)串聯(lián)的RLC電路,電容在低頻段起主導(dǎo)作用,但在自激振蕩頻率(SRF):

之后,電容的阻抗將呈現(xiàn)出電感性。由此可見,電容器只是在頻率接近或低于其SRF時(shí)才具有去耦作用,在這些頻點(diǎn)電容表現(xiàn)為低阻。

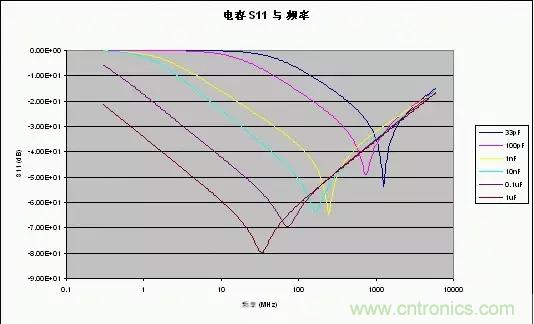

給出了不同容值下的典型S11參數(shù),從這些曲線可以清楚地看到SRF,還可以看出電容越大,在較低頻率處所提供的去耦性能越好(所呈現(xiàn)的阻抗越低)。

在Vcc星型拓?fù)涞闹鞴?jié)點(diǎn)處最好放置一個(gè)大容量的電容器,如2.2μF。該電容具有較低的SRF,對(duì)于消除低頻噪聲、建立穩(wěn)定的直流電壓很有效。IC的每個(gè)電源引腳需要一個(gè)低容量的電容器(如10nF),用來濾除可能耦合到電源線上的高頻噪聲。對(duì)于那些為噪聲敏感電路供電的電源引腳,可能需要外接兩個(gè)旁路電容。例如:用一個(gè)10pF電容與一個(gè)10nF電容并聯(lián)提供旁路,可以提供更寬頻率范圍的去耦,盡量消除噪聲對(duì)電源電壓的影響。每個(gè)電源引腳都需要認(rèn)真檢驗(yàn),以確定需要多大的去耦電容以及實(shí)際電路在哪些頻點(diǎn)容易受到噪聲的干擾。

良好的電源去耦技術(shù)與嚴(yán)謹(jǐn)?shù)腜CB布局、Vcc引線(星型拓?fù)?相結(jié)合,能夠?yàn)槿魏蜶F系統(tǒng)設(shè)計(jì)奠定穩(wěn)固的基礎(chǔ)。盡管實(shí)際設(shè)計(jì)中還會(huì)存在降低系統(tǒng)性能指標(biāo)的其它因素,但是,擁有一個(gè)“無噪聲”的電源是優(yōu)化系統(tǒng)性能的基本要素.

3、射頻PCB設(shè)計(jì)的EMC規(guī)范

1 層分布

1.1 雙面板,頂層為信號(hào)層,底面為地平面。

1.2 四層板,頂層為信號(hào)層,第二層為地平面,第三層走電源、控制線。特殊情況下(如 射頻信號(hào)線要穿過屏蔽壁),在第三層要走一些射頻信號(hào)線。每層均要求大面積敷地。

1.2 四層板,頂層為信號(hào)層,第二層為地平面,第三層走電源、控制線。特殊情況下(如 射頻信號(hào)線要穿過屏蔽壁),在第三層要走一些射頻信號(hào)線。每層均要求大面積敷地。

2 接地

2.1 大面積接地 為減少地平面的阻抗,達(dá)到良好的接地效果,建議遵守以下要求:a) 射頻 PCB 的接地要求大面積接地;b) 在微帶印制電路中,底面為接地面,必須確保光滑平整;c) 要將地的接觸面鍍金或鍍銀,導(dǎo)電良好,以降低地線最抗;d) 使用緊固螺釘,使其與屏蔽腔體緊密結(jié)合,緊固螺釘?shù)拈g距小于λ/20(依具體情 況而定)。

2.2 分組就近接地 按照電路的結(jié)構(gòu)分布和電流的大小將整個(gè)電路分為成相對(duì)獨(dú)立的幾組,各組電路就 近接地形成回路,要調(diào)整各組內(nèi)高頻濾波電容方向,縮小電源回路。注意接地線要短而直, 禁止交叉重疊,減少公共地阻抗所產(chǎn)生的干擾。

2.3 射頻器件的接地 表面貼射頻器件和濾波電容需要接地時(shí),為減少器件接地電感,要求:a) 至少要有 2 根線接鋪地銅箔;b) 用至少 2 個(gè)金屬化過孔在器件管腳旁就近接地。c) 增大過孔孔徑和并聯(lián)若干過孔。d) 有些元件的底部是接地的金屬殼,要在元件的投影區(qū)內(nèi)加一些接地孔,表面層 不得布線。

2.4 微帶電路的接地 微帶印制電路的終端單一接地孔直徑必須大于微帶線寬,或采用終端大量成排密布小孔 的方式接地。

2.5 接地工藝性要求

a) 在工藝允許的前提下,可縮短焊盤與過孔之間的距離;

b) 在工藝允許的前提下,接地的大焊盤可直接蓋在至少 6 個(gè)接地過孔上(具體數(shù)量因 焊盤大小而異);

c) 接地線需要走一定的距離時(shí),應(yīng)縮短走線長(zhǎng)度,禁止超過λ/20,以防止天線效應(yīng) 導(dǎo)致信號(hào)輻射;

d) 除特殊用途外,不得有孤立銅箔,銅箔上一定要加地線過孔;

e) 禁止地線銅箔上伸出終端開路的線頭。

3 屏蔽

3.1 射頻信號(hào)可以在空氣介質(zhì)中輻射??臻g距離越大,工作頻率越低,輸入輸出端的寄 生耦合就越小,隔離度則越大。PCB 典型的空間隔離度約為 50dB。

3.2 敏感電路和強(qiáng)烈輻射源電路要加屏蔽,但如果設(shè)計(jì)加工有難度時(shí)(如空間或成本限 制等),可不加,但要做試驗(yàn)最終決定。這些電路有:

a) 接收電路前端是敏感電路,信號(hào)很小,要采用屏蔽。

b) 對(duì)射頻單元和中頻單元須加屏蔽。接收通道中頻信號(hào)會(huì)對(duì)射頻信號(hào)產(chǎn)生較大干擾, 反之,發(fā)射通道的射頻信號(hào)對(duì)中頻信號(hào)也會(huì)造成輻射干擾。

c) 振蕩電路:強(qiáng)烈輻射源,對(duì)本振源要單獨(dú)屏蔽,由于本振電平較高,對(duì)其他單元形 成較大的輻射干擾。

d) 功放及天饋電路:強(qiáng)烈輻射源,信號(hào)很強(qiáng),要屏蔽。

e) 數(shù)字信號(hào)處理電路:強(qiáng)烈輻射源,高速數(shù)字信號(hào)的陡峭的上下沿會(huì)對(duì)模擬的射頻信 號(hào)產(chǎn)生干擾。

f) 級(jí)聯(lián)放大電路:總增益可能會(huì)超過輸出到輸入端的空間隔離度,這樣就滿足了振蕩 條件之一,電路可能自激。如果腔體內(nèi)的電路同頻增益超過 30-50dB,必須在 PCB 板 上焊接或安裝金屬屏蔽板,增加隔離度。實(shí)際設(shè)計(jì)時(shí)要綜合考慮頻率、功率、增益情況 決定是否加屏蔽板。

g) 級(jí)聯(lián)的濾波、開關(guān)、衰減電路:在同一個(gè)屏蔽腔內(nèi),級(jí)聯(lián)濾波電路的帶外衰減、級(jí) 聯(lián)開關(guān)電路的隔離度、級(jí)聯(lián)衰減電路的衰減量必須小于 30-50dB。如果超過這個(gè)值, 必須在 PCB 板上焊接或安裝金屬屏蔽板,增加隔離度。實(shí)際設(shè)計(jì)時(shí)要綜合考慮頻率、功 率、增益情況決定是否加屏蔽板。

h) 收發(fā)單元混排時(shí)應(yīng)屏蔽。

i) 數(shù)?;炫艜r(shí),對(duì)時(shí)鐘線要包地銅皮隔離或屏蔽。

4 屏蔽材料和方法

4.1 常用的屏蔽材料均為高導(dǎo)電性能材料,如銅板、銅箔、鋁板、鋁箔。鋼板或金屬鍍 層、導(dǎo)電涂層等。

4.2 靜電屏蔽主要用于防止靜電場(chǎng)和恒定磁場(chǎng)的影響。應(yīng)注意兩個(gè)基本要點(diǎn),即完善的 屏蔽體和良好的接地性。

4.3 電磁屏蔽主要用于防止交變磁場(chǎng)或交變電磁場(chǎng)的影響,要求屏蔽體具有良好的導(dǎo)電 連續(xù)性,屏蔽體必須與電路接在共同的地參考平面上,要求 PCB 中屏蔽地與被屏蔽電路地要 盡量的接近。

4.4 對(duì)某些敏感電路,有強(qiáng)烈輻射源的電路可以設(shè)計(jì)一個(gè)在 PCB 上焊接的屏蔽腔,PCB 在 設(shè)計(jì)時(shí)要加上“過孔屏蔽墻”,就是在 PCB 上與屏蔽腔壁緊貼的部位加上接地的過孔。要求 如下:

a) 有兩排以上的過孔;

b) 兩排過孔相互錯(cuò)開;

c) 同一排的過孔間距要小于λ/20;

d) 接地的 PCB 銅箔與屏蔽腔壁壓接的部位禁止有阻焊。

4.5 射頻信號(hào)線在頂層穿過屏蔽壁時(shí),要在屏蔽腔相應(yīng)位置開一個(gè)槽門,門高大于 0.5mm, 門寬要保證安裝屏蔽壁后信號(hào)線與屏蔽體間的距離大于 1mm。

5 屏蔽罩設(shè)計(jì)

5.1 金屬屏蔽腔的基本結(jié)構(gòu)

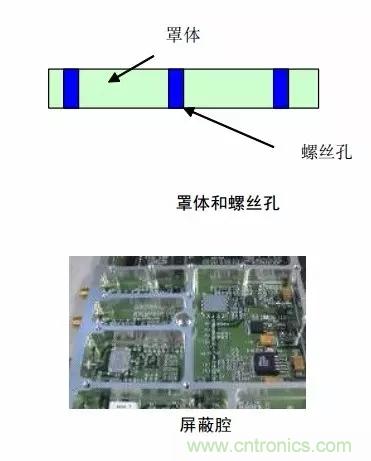

5.1.1 此類屏蔽罩被廣泛使用,如圖 27。材料一般為薄的鋁合金,制造工藝一般采用沖 壓折彎或壓力鑄造工藝,這種屏蔽罩有較多的螺釘孔,便于螺釘固定。部分需鋁合金蓋子和 吸波材料增強(qiáng)屏蔽性能。射頻 PCB 需裝在屏蔽腔內(nèi),要選擇合適的屏蔽腔尺寸,使其最低 諧振頻率遠(yuǎn)高于工作頻率,最好 10 倍以上,詳見附錄 G“金屬屏蔽腔的尺寸設(shè)計(jì)”。

5.1.2 屏蔽腔的高度一般為第一層介質(zhì)厚度 15-20 倍或以上,在屏蔽腔面積一定時(shí),要 提高屏蔽腔的最低諧振頻率,需增加長(zhǎng)寬比,避免正方形的腔體,如圖 。

5.2 金屬屏蔽腔對(duì) PCB 布局的工藝要求

5.2.1 屏蔽罩與 PCB 板接觸的罩體設(shè)計(jì)時(shí)應(yīng)考慮 PCB bottom 面的器件高度,特別是插 件器件引腳伸出的高度。

5.2.2 需考慮螺絲禁布區(qū)的大小,防止組裝時(shí)損壞表層線路或器件。射頻功放板由于結(jié) 構(gòu)尺寸的限制,其單板尺寸相對(duì)較小,故一般要求螺釘安裝空間(禁布區(qū))至少在安裝孔焊 盤外側(cè)。螺釘安裝空間見表 5

5.2.3 金屬屏蔽罩自身成本和裝配成本很貴,并且外形不規(guī)則的金屬屏蔽罩在制造時(shí)很 難保證高精度和高平整性,又使元器件布局受到一些限制;金屬屏蔽罩不利于元器件更換和 故障定位。

5.2.4 盡可能保證屏蔽罩的完整非常重要,進(jìn)入金屬屏蔽罩的數(shù)字信號(hào)線應(yīng)該盡可能走 內(nèi)層,RF 信號(hào)線可以從金屬屏蔽罩底部的小缺口和地缺口處的布線層上走出去,不過缺口 處周圍要盡可能地多布一些地,不同層上的地可通過多個(gè)過孔連在一起。

5.2.5 為保證裝配和返修,金屬屏蔽罩周圍5mm范圍內(nèi)不能有超過其高度的器件,Chip 小器件到屏蔽罩的距離應(yīng)該2mm以上,其它器件距離要求3mm以上,并且放置朝向最好 符合方便維修方向。

5.2.6 金屬屏蔽罩內(nèi)部不能有超過其高度的器件,并且器件頂部到屏蔽罩面的距離要符 合安全規(guī)范要求。

5.2.7 需考慮 SMA 微帶插座與 PCB 板接觸時(shí)的高度匹配,否則焊接可靠性存在影響。如圖29所示,設(shè)計(jì)時(shí)須考慮PCB板厚的公差(±10%),金屬屏蔽腔的加工誤差(±0.05mm)。建議 SMA 微帶插座與 PCB 板的高度間隙不超過 0.5mm,插座與焊盤不允許有明顯偏差。

5.2.8 由于功放板設(shè)計(jì)的特殊情況,容許 2 塊單板之間信號(hào)穿過屏蔽罩,并用飛線連接, 如圖

4、射頻走線與地

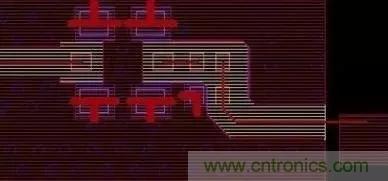

舉個(gè)例子來說吧。我們將對(duì)多層電路板進(jìn)行射頻線仿真,為了更好的做出對(duì)比,將仿真的PCB分為表層鋪地前的和鋪地后的兩塊板分別進(jìn)行仿真對(duì)比;表層未鋪地的PCB文件如下圖1所示(兩種線寬):

圖1a:線寬0.1016 mm的射頻線(表層鋪地前)

圖1b:線寬0.35 mm的射頻線(表層鋪地前)

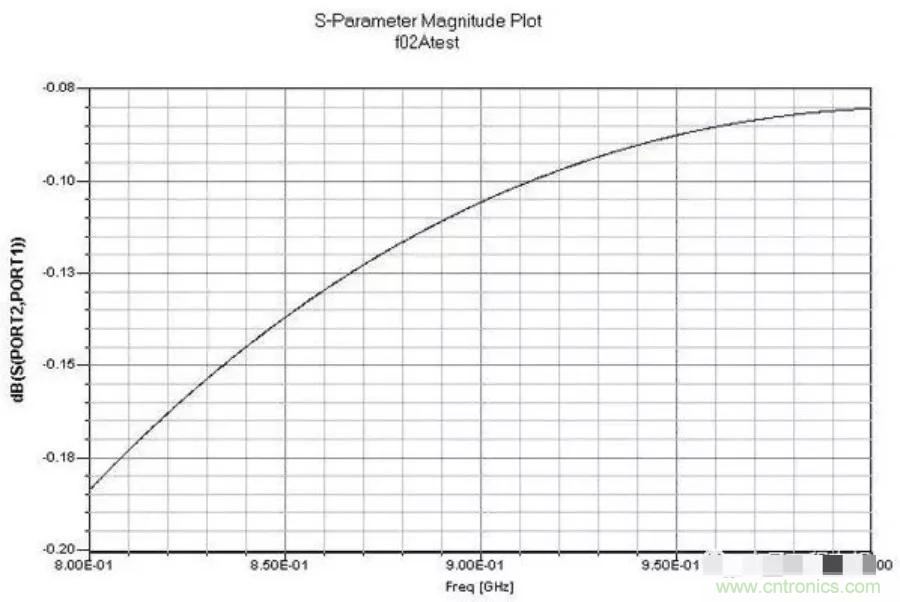

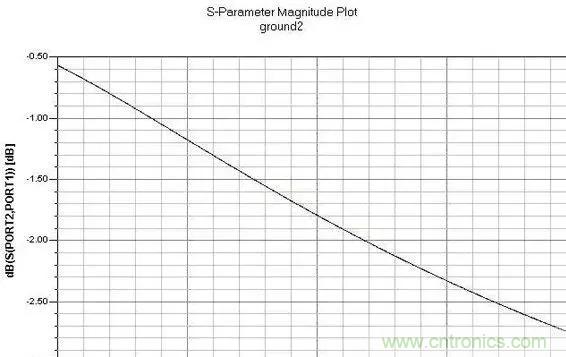

首先將線寬不同的兩塊板(表層鋪地前)由ALLEGRO導(dǎo)入SIWAVE,在目標(biāo)線上加入50Ω端口。針對(duì)不同線寬0.1016mm和0.35mm, 我們的仿真結(jié)果如圖2所示,圖中顯示的曲線是S21,仿真頻率范圍為800MHz-1GHz。

圖2a:表層未鋪地的S21 (線寬0.1016mm)

圖2b:表層未鋪地的S21 (線寬0.35mm)

由圖中可以看到,在800MHz-1GHz的范圍內(nèi),仿真的數(shù)據(jù)展示為小數(shù)點(diǎn)后一到兩位的數(shù)量級(jí),0.35mm的損耗要比0.1016mm的線小一個(gè)數(shù)量 級(jí),這是因?yàn)?.35mm的線寬在該板的層疊條件下其特征阻抗接近50Ω。因此間接驗(yàn)證了我們所做的阻抗計(jì)算(用線寬約束)是有一定作用的。

接下來我們做了表層鋪地后的同樣的仿真(800MHz-1GHz),導(dǎo)入的PCB文件如下圖。

圖3a:0.1016 mm的射頻線(表層鋪地)

圖3b:0.35 mm的射頻線(表層鋪地)

圖3:表層鋪過地后的PCB

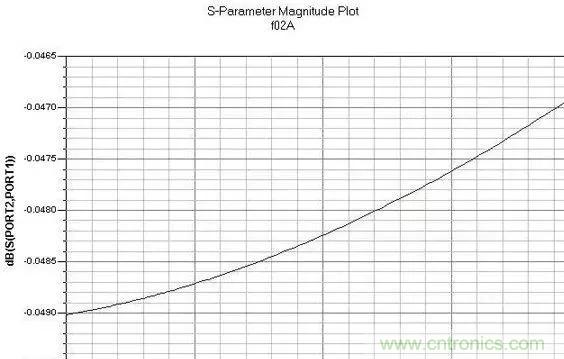

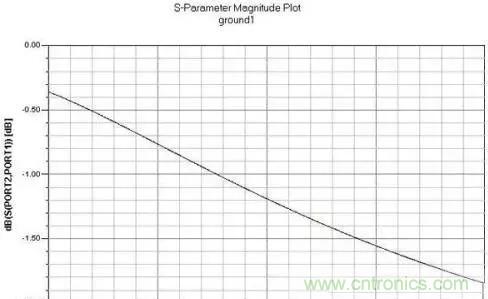

仿真結(jié)果如下圖:

圖4a:表層鋪地后的S21 (0.1016mm)

圖4b:表層鋪地后的S21 (0.35mm)

圖4:表層鋪過地后的S21

由圖中看到,仿真的數(shù)據(jù)顯示,該傳輸線的線損已經(jīng)是1-2 dB的數(shù)量級(jí)了,當(dāng)然0.35 mm的損耗要明顯小于0.1016 mm的。另外一個(gè)明顯的現(xiàn)象是相對(duì)于未鋪地的仿真結(jié)果,隨著頻率由800MHz到1GHz的增加,損耗趨大。

我們可以從仿真的結(jié)果中得到這樣一個(gè)結(jié)果:

1.射頻走線最好按50歐姆走,可以減小線損;

2.表層的鋪地事實(shí)上是將一部分RF信號(hào)能量耦合到了地上,造成了一定的損耗。因此PCB表層的鋪地應(yīng)該有所講究。盡量遠(yuǎn)離RF線。工程經(jīng)驗(yàn)是大于1.5倍的線寬。

【5】設(shè)計(jì)checklist

一、布局注意事項(xiàng)

(1) 結(jié)構(gòu)設(shè)計(jì)要求 在 PCB 布局之前需要弄清楚產(chǎn)品的結(jié)構(gòu)。

結(jié)構(gòu)需要在 PCB 板上體現(xiàn)出來。比如腔殼的外邊厚度大小,中間隔腔的厚度大小, 倒角半徑大小和隔腔上的螺釘大小等等(換句話說,結(jié)構(gòu)設(shè)計(jì)是根據(jù) 完成后的 PCB 上所畫的輪廓(結(jié)構(gòu)部分)進(jìn)行具體設(shè)計(jì)的)。一般情 況,外邊腔厚度為 4mm;內(nèi)腔寬度為 3mm;點(diǎn)膠工藝的為 2mm;倒角 半徑 2.5mm。以 PCB 板的左下角為原點(diǎn),隔腔需在柵格 0.5 的整數(shù)倍, 最少需要做到柵格為 0.1 的整數(shù)倍。這樣有利于結(jié)構(gòu)加工商進(jìn)行加工, 誤差控制比較精確些。當(dāng)然,這需要根據(jù)客戶的要求來設(shè)計(jì)。

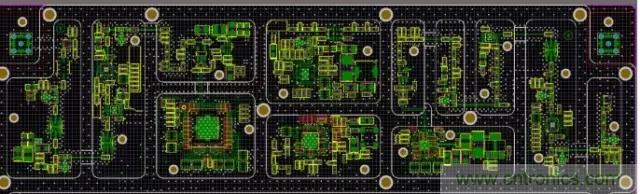

下圖所示為 PCB 設(shè)計(jì)完成后的結(jié)構(gòu)輪廓圖:

(2) 布局要求 布局優(yōu)先對(duì)射頻鏈路進(jìn)行布局,然后對(duì)其它電路進(jìn)行布局。A 射頻鏈路布局注意事項(xiàng) 完全根據(jù)原理圖的先后順序(輸入到輸出,包括每個(gè)元件的先后 位置和元件與元件之間的間距都有講究的。有的元件與元件之間距離 不宜過大,比如π 網(wǎng)。)進(jìn)行布局,布局成“一”字形或者“L”形。在實(shí)際的射頻鏈路布局中,因受產(chǎn)品的空間限制,不可能完全實(shí) 現(xiàn),這就迫使我們將布局成“U”形。布局成 U 形并不是不可以,但 需要在中間加隔腔將其左右進(jìn)行隔離,做好屏蔽。

還有一種在橫向也需要添加隔腔。即,用隔腔把一字形左右進(jìn)行 隔離。這主要是因?yàn)樾枰綦x部分非常敏感或易干擾其它電路;另外, 還有一種可能就是一字形輸入端到輸出端這段電路的增益過大,也需 要用隔腔將其分開(若增益過大,腔體太大,可能會(huì)引起自激。)。

B 芯片外圍電路布局 射頻器件外圍電路布局嚴(yán)格參照 datasheet 上面的要求進(jìn)行布 局,受空間限制可以進(jìn)行調(diào)整;數(shù)字芯片外圍電路布局就不多講了。

二、 布線注意事項(xiàng)

根據(jù) 50 歐姆阻抗線寬進(jìn)行布線,盡量從焊盤中心出線,線成直 線,盡量走在表層。在需要拐彎的地方做成 45 度角或圓弧走線,推 薦在電容或電阻兩邊進(jìn)行拐彎。如果遇到器件走線匹配要求的,請(qǐng)嚴(yán) 格按照 datasheet 上面的參考值長(zhǎng)度走線。比如,一個(gè)放大管與電容 之間的走線長(zhǎng)度(或電感之間的走線長(zhǎng)度)要求等等。

在進(jìn)行 PCB 設(shè)計(jì)時(shí),為了使高頻電路板的設(shè)計(jì)更合理,抗干擾性能更 好,應(yīng)從以下幾方面考慮(通用做法):

(1) 合理選擇層數(shù) 在 PCB 設(shè)計(jì)中對(duì)高頻電路板布線時(shí),利用中間內(nèi)層平面作為電源和 地線層,可以起到屏蔽的作用,有效降低寄生電感、縮短信號(hào)線長(zhǎng)度、 降低信號(hào)間的交叉干擾。

(2) 走線方式 走線必須按照 45°角拐彎或圓弧拐彎,這樣可以減小高頻信 號(hào)的發(fā)射和相互之間的耦合。

(3) 走線長(zhǎng)度 走線長(zhǎng)度越短越好,兩根線并行距離越短越好。

(4) 過孔數(shù)量 過孔數(shù)量越少越好。

(5) 層間布線方向 層間布線方向應(yīng)該取垂直方向,就是頂層為水平方向,底層為 垂直方向,這樣可以減小信號(hào)間的干擾。

(6) 敷銅 增加接地的敷銅可以減小信號(hào)間的干擾。

(7) 包地 對(duì)重要的信號(hào)線進(jìn)行包地處理,可以顯著提高該信號(hào)的抗干擾 能力,當(dāng)然還可以對(duì)干擾源進(jìn)行包地處理,使其不能干擾其他 信號(hào)。

(8) 信號(hào)線 信號(hào)走線不能環(huán)路,需要按照菊花鏈方式布線。

三、 接地處理

(1)射頻鏈路接地 射頻部分采用多點(diǎn)接地方式進(jìn)行接地處理。射頻鏈路鋪銅間隙一般 30mil 到 40mil 用的比較多。兩邊都需要打接地孔,且間距盡量保持 一致。射頻通路上對(duì)地電容電阻的接地焊盤,盡量就近打接地孔。器 件上的接地焊盤都需要打接地過孔。

(2)腔殼接地孔 為了讓腔殼與 PCB 板之間更好的接觸。一般打兩排接地孔且交錯(cuò)方 式放置,如圖 06 所示。PCB 隔腔上需要開窗,如圖 07 所示。PCB 底 層接地銅皮與底板接觸的地方都需要開窗處理,使其更好的接觸。如 圖 08 所示(PCB 板的上半部分與底座接觸):

PCB 隔腔接地過孔圖

PCB 隔腔開窗圖

PCB 底層開窗圖

(3)螺釘放置(需要了解結(jié)構(gòu)知識(shí)) 為了使 PCB 與底座和腔殼之間有更緊密的接觸(更好的屏蔽) 需要在 PCB 板上放置螺釘孔位置。PCB 與腔殼之間螺釘放置方法:隔腔每個(gè)交叉的地方放置一個(gè)螺 釘。在實(shí)際設(shè)計(jì)中,比較難實(shí)現(xiàn),可以根據(jù)模塊電路功能進(jìn)行適當(dāng)調(diào) 整。但不管怎樣,腔殼四個(gè)角上必須都有螺釘。

腔殼螺釘圖

PCB 與底座之間的螺釘放置方法:腔殼中的每個(gè)小腔內(nèi)都需要有 螺釘,視腔大小而定螺釘數(shù)量(腔越大,放置的螺釘就多)。一般原 則是在腔的對(duì)角上放置螺釘。SMA 頭或其他連接器旁邊必須放置螺釘。在 SMA 頭或連接器在插拔過程中不致 PCB 板變形。

腔內(nèi)螺釘圖