【導(dǎo)讀】1958年,德州儀器公司用兩個(gè)晶體管制造了第一個(gè)集成電路觸發(fā)器���。今天的芯片包含超過10億個(gè)晶體管���。曾經(jīng)可以支撐整個(gè)公司會(huì)計(jì)系統(tǒng)的記憶,現(xiàn)在變成了一個(gè)十幾歲的年輕人在智能手機(jī)里攜帶的內(nèi)存���。這種規(guī)模的增長(zhǎng)源于晶體管數(shù)量的不斷擴(kuò)大和硅制造工藝的改進(jìn)���。

一、 歷史:

真空管的發(fā)明開創(chuàng)了電子工業(yè)��。這些裝置將控制真空中電子的流動(dòng)����。但是,在第二次世界大戰(zhàn)之后,人們發(fā)現(xiàn)由于大量的分立元件�����,這些器件的復(fù)雜性和功耗都在顯著增加���。結(jié)果��,這些設(shè)備的性能會(huì)持續(xù)下降�����。其中一個(gè)例子是波音B-29��,在戰(zhàn)爭(zhēng)期間����,它將由300-1000個(gè)真空管組成�。每增加一個(gè)部件都會(huì)降低可靠性并增加故障排除時(shí)間。

1947年�����,貝爾實(shí)驗(yàn)室的約翰·巴登�、威廉·肖克利和沃特·布拉坦公布了第一臺(tái)工作正常的點(diǎn)接觸鍺晶體管�,這是一項(xiàng)重大突破����。1950年,肖克利發(fā)明了第一個(gè)雙極結(jié)晶體管(BJT)���。與真空管相比�����,晶體管更可靠��、更省電��、體積更小����。晶體管是一個(gè)三端器件���,可以看作是一個(gè)電控開關(guān)。其中一個(gè)終端充當(dāng)控制終端��。理想情況下����,如果電流被施加到控制終端上�����,則該設(shè)備將充當(dāng)兩個(gè)終端之間的閉合開關(guān)���,而這兩個(gè)終端則表現(xiàn)為一個(gè)開路開關(guān)。1958年����,德克薩斯儀器公司的杰克·基爾比制造了第一個(gè)集成電路,由兩個(gè)雙極晶體管連接在一塊硅上�,由此開創(chuàng)了“硅時(shí)代”。早期的集成電路使用雙極結(jié)晶體管�。BJT的一個(gè)缺點(diǎn)是由于較大的靜態(tài)功耗。這意味著即使在電路沒有開的情況下��,電能也會(huì)被消耗掉�。這限制了可以集成到單個(gè)硅芯片中的晶體管的最大數(shù)量。

1963年����,F(xiàn)airchild的frankwanlass和C.T.Sah公布了第一個(gè)邏輯門,其中n溝道和p溝道晶體管被用在互補(bǔ)對(duì)稱電路結(jié)構(gòu)中�。這就是今天所說的CMOS�。它的靜態(tài)功耗幾乎為零�����。

早期的集成電路使用NMOS技術(shù)�,因?yàn)镹MOS工藝相當(dāng)簡(jiǎn)單,成本較低��,而且與CMOS技術(shù)相比��,可以將更多的器件封裝到單個(gè)芯片中��。第一個(gè)微處理器是由英特爾公司在1971年宣布的�。

由于NMOS晶體管的靜態(tài)功耗要比CMOS大得多,上世紀(jì)80年代�����,成千上萬的晶體管被集成到一個(gè)芯片上��,集成電路的功耗成為一個(gè)嚴(yán)重的問題�。由于低功耗���、性能可靠���、速度快等特點(diǎn)��,CMOS技術(shù)將在幾乎所有的數(shù)字應(yīng)用中采用并取代NMOS和雙極技術(shù)���。

在接下來的幾年里,隨著芯片封裝密度和微電子產(chǎn)品的性能成本比的進(jìn)一步提高���,CMOS的規(guī)?�;凸に嚰夹g(shù)的改進(jìn)使電路速度不斷提高��。

在這里�����,我們討論體硅CMOS技術(shù)�����,縮放的必要性和重要性���,他們的各種影響和相關(guān)的解決方案。我們還討論了晶體管材料和任何先進(jìn)技術(shù)節(jié)點(diǎn)中使用的新材料的物理縮放限制���。如今�����,由于在32nm以下的技術(shù)節(jié)點(diǎn)遇到了各種限制�,業(yè)界正在從使用規(guī)劃器晶體管技術(shù)開始。我們討論了新的器件結(jié)構(gòu):SOI和FinFET取代了planner體晶體管���。

二 MOSFET器件概述:

在這里��,我們首先討論CMOS核心單元MOSFET或簡(jiǎn)單MOS的基本結(jié)構(gòu)����、工作原理和重要術(shù)語�����。第一個(gè)成功的MOS晶體管將使用金屬作為柵極材料��,SiO2(氧化物)用作絕緣體��,半導(dǎo)體用作襯底��。因此,這種器件被命名為MOS晶體管�。場(chǎng)效應(yīng)晶體管(FET)這個(gè)名字是指當(dāng)一個(gè)電場(chǎng)通過柵極氧化物時(shí)�����,由晶體管打開和關(guān)閉柵極��。

MOS結(jié)構(gòu):

根據(jù)導(dǎo)電溝道的類型�����,可以看出兩種MOS結(jié)構(gòu):n溝道MOS和p溝道MOS��。在這里�,我們將只概述NMOS晶體管,因?yàn)檫@兩個(gè)晶體管本質(zhì)上是互補(bǔ)的�。

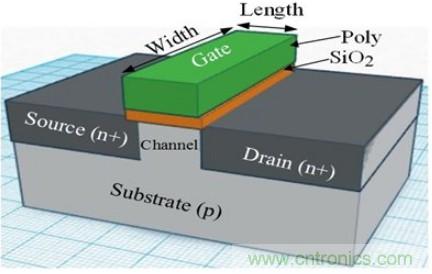

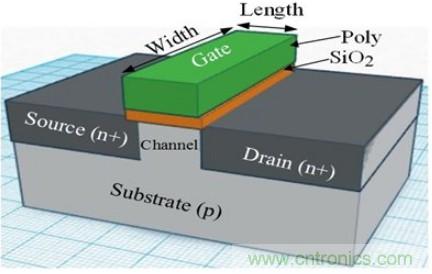

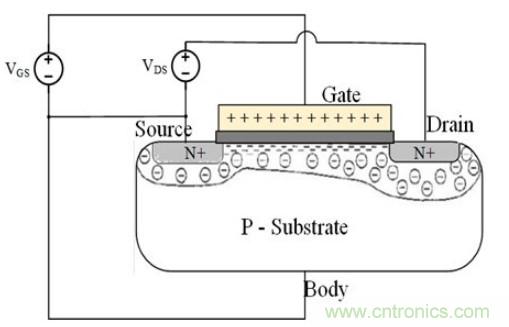

MOS晶體管是一種具有終端漏極、源極�����、柵極和襯底的四端器件����。圖1顯示了NMOS的三維結(jié)構(gòu)。NMOS晶體管形成在p型硅襯底(也稱為主體)上。在裝置的頂部中心部分��,形成一個(gè)低阻電極����,該電極通過絕緣體與主體分離。通常采用n型或p型重?fù)诫s的多晶硅作為柵極材料���。在這里����,二氧化硅(二氧化硅或簡(jiǎn)單的氧化物)被用作絕緣體�����。通過將施主雜質(zhì)注入襯底的兩側(cè)�����,形成源和漏����。在圖1中,這些區(qū)域用n+表示����,表示施主雜質(zhì)的重?fù)诫s����。這種重?fù)诫s導(dǎo)致這些區(qū)域的低電阻率��。

如果兩個(gè)n+區(qū)在不同的電位下偏壓�����,低電位的n+區(qū)將作為源區(qū)�,而另一個(gè)區(qū)將作為漏區(qū)���。因此��,漏極和源極可以根據(jù)施加在它們上的電位互換�����。源極和漏極之間的區(qū)域被稱為寬度為W���,長(zhǎng)度為L(zhǎng)的溝道,它在決定MOS晶體管的特性方面起著重要的作用����。

MOS工作原理:

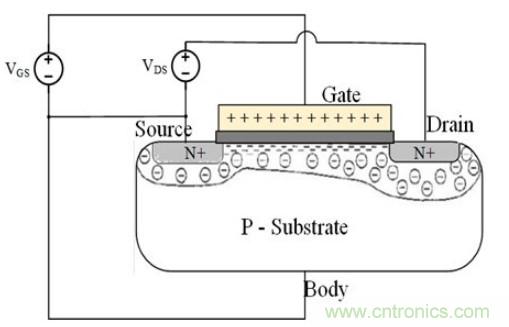

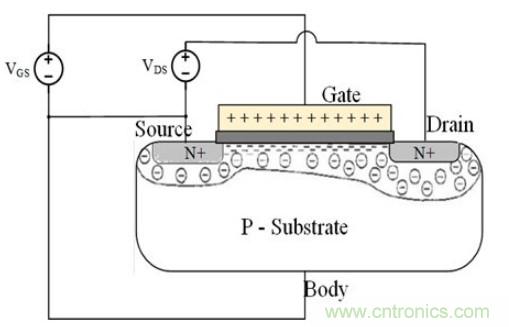

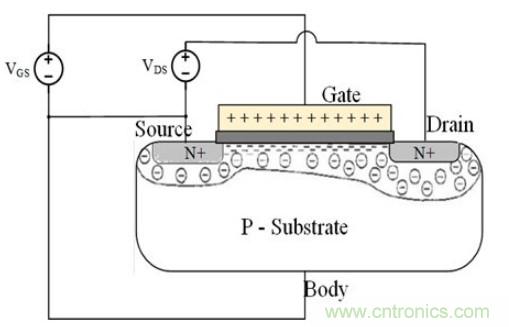

對(duì)于MOS晶體管�,柵極電壓決定漏極和源極之間的電流是否會(huì)流動(dòng)�。讓我們進(jìn)一步看。當(dāng)一個(gè)足夠正的Vgs電壓施加到nmo的柵極上時(shí)�����,正電荷被放置在柵極上�,如圖3所示。這些正電荷將排斥p型襯底的多數(shù)載流子����,即襯底上的空穴,留下負(fù)電荷受體離子�����,形成耗盡區(qū)�����。如果我們進(jìn)一步增加Vgs�,在某個(gè)電位水平上,它甚至?xí)贡砻嫖娮?����。因此,大量的電子被吸引到表面���。這種情況被稱為反型�����,因?yàn)閜型襯底的表面通常有大量的空穴,而溝道中有大量的電子�����。

漏極到襯底和源極到襯底保持反向偏壓�����。在圖2中��,源到體保持零偏差��。由于漏極電位比源極電位更為正�,因此與源側(cè)相比,漏體間的反向偏壓更大����,導(dǎo)致漏極區(qū)下的耗盡層更深�。

當(dāng)正電位通過漏極施加到源極時(shí)��,電子從源極流過導(dǎo)電通道���,并從漏極形成電流流出���。因此,正電流Id從漏極流向源�。

圖2 NMOS晶體管的反型層

推薦閱讀: