【導(dǎo)讀】有時我們會忽略使用去耦的目的,僅僅在電路板上分散大小不同的許多電容,使較低阻抗電源連接到地。但問題依舊:需要多少電容?許多相關(guān)文獻表明,必須使用大小不同的許多電容來降低功率傳輸系統(tǒng)(PDS)的阻抗,但這并不完全正確。相反,僅需選擇正確大小和正確種類的電容就能降低PDS阻抗。

舉個例子

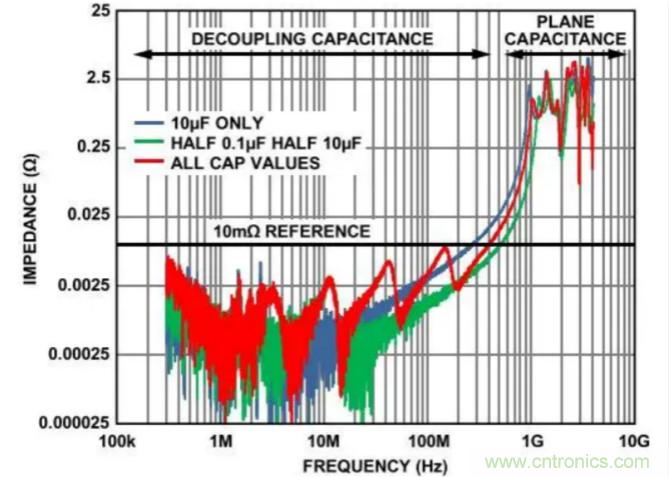

考慮設(shè)計一個10 mΩ參考層,如圖1所示。如紅色曲線所示,系統(tǒng)電路板上使用許多不同值的電容,0.001 μF、0.01 μF、0.1 μF等等。這當然可以降低500 MHz頻率范圍內(nèi)的阻抗,但是,請看綠色曲線,同樣的設(shè)計僅使用0.1 μF和10 μF電容。這證明,如果使用正確的電容,則不需要如此多的電容。這也有助于節(jié)省空間和物料(BOM)成本。

圖1. 電容示例

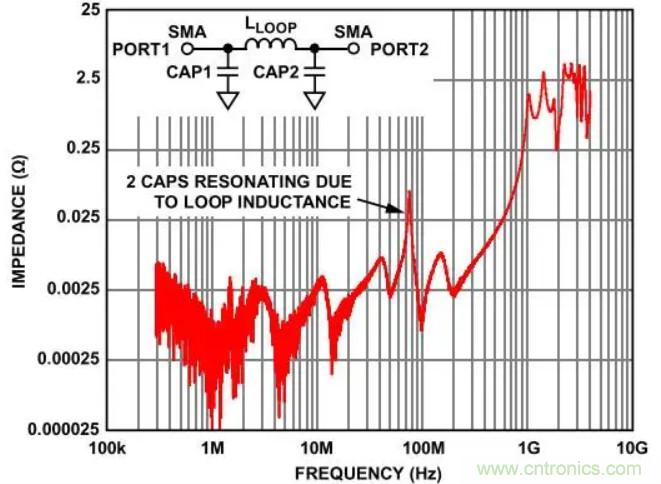

注意,并非所有電容“生而平等”,即使同一供應(yīng)商,工藝、尺寸和樣式也有差別。如果未使用正確的電容,不論是多個電容還是幾個不同類型,都會給PDS帶來反作用。結(jié)果可能是形成電感環(huán)路。電容放置不當或者使用不同工藝和型號的電容(因而對系統(tǒng)內(nèi)的頻率做出不同響應(yīng)),彼此之間可能會發(fā)生諧振,見圖2。

圖2. 諧振電容

所以,了解系統(tǒng)所用電容類型的頻率響應(yīng)很重要。隨便選用電容,會讓設(shè)計低阻抗PDS系統(tǒng)的努力付之東流。

如何設(shè)計出合格的PDS

要設(shè)計出合格的PDS,需要使用各種電容(見圖1)。PCB上使用的典型電容值只能將直流或接近直流頻率至約500 MHz范圍的阻抗降低。高于500 MHz頻率時,電容取決于PCB形成的內(nèi)部電容。注意,電源層和接地層緊密疊置會有幫助。

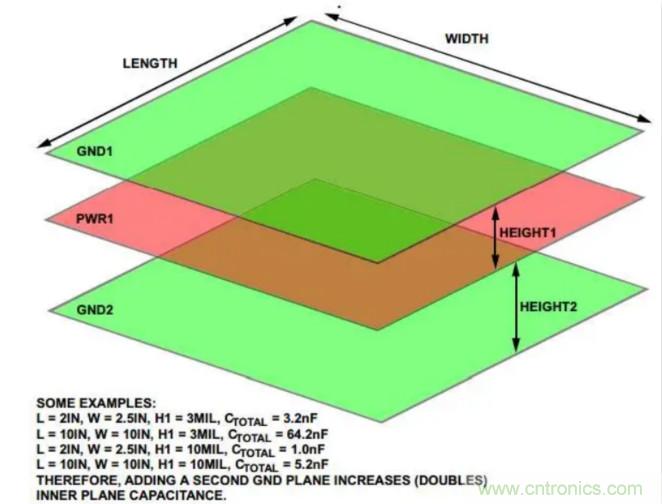

應(yīng)當設(shè)計一個支持較大層電容的PCB層疊結(jié)構(gòu)。例如,六層堆疊可能包含頂部信號層、第一接地層、第一電源層、第二電源層、第二接地層和底部信號層。規(guī)定第一接地層和第一電源層在層疊結(jié)構(gòu)中彼此靠近,這兩層間距為2到4密爾,形成一個固有高頻層電容。此電容的最大優(yōu)點是它是免費的,只需在PCB制造筆記中注明。如果必須分割電源層,同一層上有多個VDD電源軌,則應(yīng)使用盡可能大的電源層。不要留下空洞,同時應(yīng)注意敏感電路。這將使該VDD層的電容最大。

如果設(shè)計允許存在額外的層(上例中,從六層變?yōu)榘藢樱?,則應(yīng)將兩個額外的接地層放在第一和第二電源層之間。在核心間距同樣為2到3密爾的情況下,此時層疊結(jié)構(gòu)的固有電容將加倍,示例見圖3。

圖3. 高頻層電容示例

與添加更多分立高頻電容以在高頻時保持低阻抗相比,此結(jié)構(gòu)更易于設(shè)計。

PDS的任務(wù)是將響應(yīng)電源電流需求而產(chǎn)生的電壓紋波降至最低,這點很重要但常被忽略。所有電路都需要電流,有些電路需求量較大,有些電路則需要以較快的速率提供電流。采用充分去耦的低阻抗電源層或接地層以及良好的PCB層疊,有助于將因電路的電流需求而產(chǎn)生的電壓紋波降至最低。例如,根據(jù)所用的去耦策略,如果系統(tǒng)設(shè)計的開關(guān)電流為1 A,PDS的阻抗為10 mΩ,則最大電壓紋波為10 mV。計算很簡單:V = IR。

憑借完美的PCB堆疊,可覆蓋高頻范圍,同時在電源層起始入口點和高功率或浪涌電流器件周圍使用傳統(tǒng)去耦,可覆蓋低頻范圍(<500 MHz)。這可確保PDS阻抗在整個頻率范圍內(nèi)均最低。沒有必要各處都配置電容;電容正對著每個IC放置會破壞許多制造規(guī)則。如果需要這種嚴厲的措施,則說明電路存在其它問題。

推薦閱讀: