【導讀】模擬電路設計師在設計放大器時,為了使其穩(wěn)定,煞費苦心。然而在真實世界中,總是有很多情況引起放大器振蕩——不同類型的負載可能使放大器振鳴;設計不當?shù)姆答伨W(wǎng)絡可能引起不穩(wěn)定性;電源旁路不夠充分也可能引起問題;輸入和輸出作為單端口系統(tǒng)也還可能自振蕩……

為了解決這些問題,今天我們將同大家共同探討振蕩的常見原因以及補救方法。

基礎知識

圖 1a 顯示了一個非軌至軌放大器的方框圖。輸入控制 gm 方框,gm 方框驅(qū)動增益節(jié)點,并在輸出端得到緩沖。補償電容器 Cc 是主要的頻率響應組件。Cc 的返回引腳應該接地,如果有這樣一個引腳的話;但是運算放大器傳統(tǒng)上不接地,電容器電流會返回一個或兩個電源。圖 1b 是最簡單的軌至軌輸出放大器的方框圖。輸入方框 gm 的輸出電流通過“電流耦合器”發(fā)送,這將驅(qū)動電流分成兩部分,提供給輸出晶體管。頻率響應由兩個 Cc/2s 決定,二者實際上是并聯(lián)的。

圖1a:典型非軌至軌運算放大器拓撲

圖1b:典型軌至軌運算放大器拓撲

以上兩種拓撲代表了絕大多數(shù)使用外部反饋的運算放大器。圖 1c 顯示了我們的理想放大器的頻率響應,盡管兩個電路的電氣原理不同,但行為表現(xiàn)卻類似。由 gm 和 Cc 形成的單極點補償提供 GBF = gm/(2πCc) 的單位增益帶寬積頻率。在 GBF/Avol 附近,這些放大器的相位滯后從 –180° 降至 –270°,其中 Avol 是放大器開環(huán) DC 增益。當頻率遠高于這個低頻率時,相位就一直停在 –270° 上。這就是為人熟知的“主極點補償”,其中 Cc 極點主導頻率響應,隱藏了有源電路的各種頻率限制。

圖1c:理想化的運算放大器頻率響應

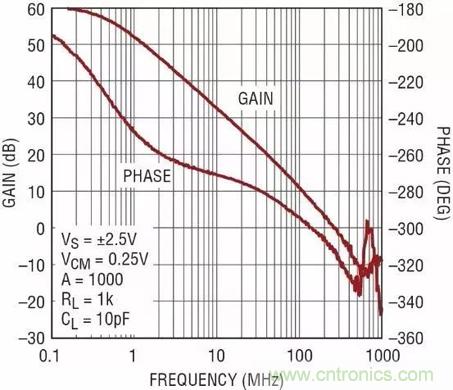

圖 2 顯示了 LTC6268 放大器隨頻率變化的開環(huán)增益和相位響應。LTC6268是一款小巧的小型低噪聲 500MHz 放大器,具軌至軌輸出和僅 3fA 偏置電流,可以作為一個很好的例子來說明真實放大器的行為表現(xiàn)。主極點補償?shù)?–90° 相位滯后約從 0.1MHz 開始,在 8MHz 左右達到 –270°,超過 30MHz 時則下移超過 –270°。實際上,除了由于額外增益級和輸出級所引起的基本主導補償滯后之外,所有的放大器都具有高頻相位滯后。通常,額外相位滯后的起點在 GBF/10 左右。

圖2:LTC6268的增益和相位隨頻率的變化

反饋的穩(wěn)定性是一個繞環(huán)路增益和相位的問題,或者,Avol 乘以反饋系數(shù),簡言之就是環(huán)路增益。如果我們以單位增益配置方式連接 LTC6268,那么輸出電壓 100% 反饋回來。在非常低的頻率上,輸出是“–”輸入的負值,或相位滯后 –180°。補償通過放大器又增加了 -90° 滯后,從“–”輸入到輸出引入 –270° 滯后。當環(huán)路相位滯后增大到 ±360° 或其倍數(shù)時,就會發(fā)生振蕩,而且環(huán)路增益至少是 1V/V 或 0dB。相位裕度是衡量當增益為 1V/V 或 0dB 時相位滯后與 360° 相差多少。圖 2 顯示,在 130MHz 時相位裕度約為 70°(10pF 紅色曲線)。這是一個非常健康的數(shù)字,相位裕度低至大約 35° 都是可行的。

一個不太常提及的話題是增益裕度,盡管這是個同樣重要的參數(shù)。當相位裕度在一些較高的頻率上降低至零時,如果增益至少為 1V/V 或 0dB,放大器就會振蕩。如圖 2 所示,當相位降至 0° (或 360° 的倍數(shù),或如圖中所示為 –180°) 時,增益在 1GHz 左右約為 –24dB。這是非常低的增益,在這種頻率上不會發(fā)生振蕩。實際上,人們希望增益裕度至少為 4dB。

去補償型放大器

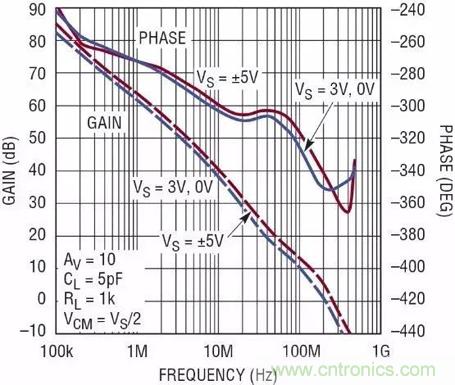

雖然 LTC6268 在單位增益條件下是相當穩(wěn)定的,但是有少量故意不穩(wěn)定的運放。通過把放大器補償設計為僅在較高閉環(huán)增益下保持穩(wěn)定,設計折衷能夠提供比單位增益補償方案更高的轉(zhuǎn)換速率、更寬的 GBF、和更低的輸入噪聲。圖 3 示出了 LTC6230-10 的開環(huán)增益和相位。該放大器打算在數(shù)值為 10 或更大的反饋增益條件下使用,因此反饋網(wǎng)將至少使輸出衰減 10 倍。通過這個反饋網(wǎng)絡,我們可以找到開環(huán)增益為 10V/V 或 20dB 時的頻率,并發(fā)現(xiàn)在 50MHz (±5V 電源) 時相位裕度為 58°。單位增益時,相位裕度僅約 0°,放大器會振蕩。

圖3:LT6230-10的增益和相位隨頻率的變化

一個觀察結(jié)果是,當提供比最小穩(wěn)定增益大的閉環(huán)增益時,所有放大器都會更穩(wěn)定。即使 1.5 的增益也會使單位增益可穩(wěn)定的放大器穩(wěn)定得多。

反饋網(wǎng)絡

談到振蕩,反饋網(wǎng)絡本身可也能引起振蕩。請注意,在圖 4 中,我們放上了一個與反饋分壓器并聯(lián)的寄生電容。這是不可避免的,電路板上每個組件的每個端子到地都有約 0.5pF 寄生電容,還有走線的寄生電容。

圖4:寄生電容加載到反饋網(wǎng)絡上

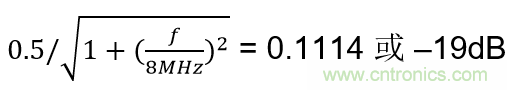

實際上,節(jié)點的最小電容為 2pF,每英寸走線也有約 2pF 電容。累積寄生電容很容易達到 5pF??紤]提供 +2 增益的 LTC6268。為了降低功率,我們將 Rf 和 Rg 的值設定為相當高的 10kΩ。Cpar = 4pF 時,反饋網(wǎng)絡在 1/(2π*Rf||Rg*Cpar) 或 8MHz 上有一個極點。利用反饋網(wǎng)絡的相位滯后為 –atan(f/8MHz) 這個事實,我們可以估計出,在 35MHz 左右,環(huán)路將有 360° 的相位滯后,這時放大器的相位滯后為 –261°,反饋網(wǎng)絡滯后 –79°。在這一相位和頻率上,放大器仍有 22dB 增益,同時分壓器增益為

在 0° 相位上,放大器的 22dB 乘以反饋分壓器的 –19dB 產(chǎn)生 +3dB 環(huán)路增益,電路振蕩。為了在存在寄生電容的情況下正常運行,我們必須將反饋電阻器的值調(diào)小,這樣反饋極點才能遠遠超過環(huán)路的單位增益頻率。極點與 GBF 之比至少為 6 倍才行。

運算放大器輸入端本身可能也有相當大的電容,與 Cpar 一樣。尤其是,低噪聲和低 Vos 放大器有大型輸入晶體管,可能比其他類型的放大器有更大的輸入電容,而輸入電容加載到了放大器反饋網(wǎng)絡上。我們需要查閱數(shù)據(jù)表,以了解將有多大的電容與 Cpar 并聯(lián)。幸運的是,LT6268 僅有 0.45pF 電容,對這樣一個低噪聲放大器而言,這個電容值已經(jīng)非常低了。可用 ADI 免費提供的、運行于 LTspice® 上的宏模型模擬有寄生電容的電路。

圖 5 顯示了提高分壓器電容容限的方法。

圖5:降低Cpar影響的方法

圖 5a 顯示了一款非負輸出放大器配置,增加了 Rin。假定 Vin 是低阻抗源 (<

圖 5b 顯示了一種負輸出配置。Rg 仍然執(zhí)行環(huán)路衰減而不改變閉環(huán)增益。在這種情況下,輸入阻抗不受“Rg”干擾,但噪聲、失調(diào)和帶寬參數(shù)會惡化。

圖 5c 示出了在同相放大器中補償 Cpar 的優(yōu)選方法。如果我們設定 Cf* Rf = Cpar * Rg,則我們擁有了一個“補償衰減器”,從而使反饋分壓器現(xiàn)在于所有頻率下都具有相同的衰減,并且解決了 Cpar 問題。產(chǎn)品中的失配將在放大器的通帶中引起“凸塊”,和在響應曲線中引起“擱板”(此時,低頻響應是平坦的,但是在 f = 1/2 * Cpar * Rg 附近變至另一個平直線段)。圖 5d 示出了用于負輸出放大器的等效 Cpar 補償。必需對頻率響應進行分析以找到一個正確的 Cf,而放大器的帶寬即為該分析工作的一部分。

這里依次列舉一些有關(guān)電流反饋放大器 (CFA) 的評論。如果圖 5a 中的放大器是一個 CFA,則“Rin”對于更改頻率響應所起的作用甚微,因為負輸入是非常低的阻抗并主動地拷貝正輸入。噪聲指標將略有劣化,而且額外的負輸入偏置電流實際上將以 Vos/Rin 的形式出現(xiàn)。同樣,就頻率響應而言,圖 5b 中的電路未被“Rg”所改變。反相輸入并不僅僅是一個虛擬地,它是一個真正的接地低阻抗,而且已經(jīng)容許了 Cpar (僅限負輸出模式!)。DC 誤差類似于圖 5a 中所示的情形。圖 5c 和 5d 對于電壓輸入運放可能是優(yōu)選方案,但是 CFA 完全不能容許一個沒有振蕩的直接反饋電容器。

負載問題

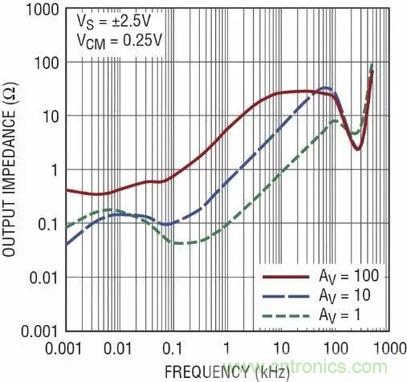

就像反饋電容可能損害相位裕度一樣,負載電容也能起到同樣的作用。圖 6 顯示在幾種增益設定值情況下,LTC6268 輸出阻抗隨頻率的變化。請注意,單位增益輸出阻抗低于較高增益時的輸出阻抗。全反饋使開環(huán)增益能夠降低放大器的固有輸出阻抗。因此圖 6 中,增益為 10 時的輸出阻抗一般是單位增益時輸出阻抗的 10 倍。由于反饋衰減器降低了環(huán)路增益,繞環(huán)路增益為 1/10,否則就會降低閉環(huán)輸出阻抗。開環(huán)輸出阻抗約為 30,這一點在增益為 100 這條曲線的高頻平坦區(qū)域很明顯。在這個區(qū)域,從增益帶寬頻率/100 左右到增益帶寬頻率,沒有足夠的環(huán)路增益來降低開環(huán)輸出阻抗。

圖6:在3種增益情況下,LTC6268輸出阻抗隨頻率的變化

電容器負載會引起開環(huán)輸出阻抗相位滯后和幅度衰減。例如,一個 50pF 負載和我們的 LTC6268 30 輸出阻抗形成了另一個位于 106MHz 的極點,輸出在此具有一個 –45° 相位滯后和 –3dB 衰減。在該頻率,放大器具有一個 –295° 相位和 10dB 增益。假設采用的是單位增益反饋,我們并未完全實現(xiàn)振蕩,因為相位未使之至 ±360° (在 106MHz)。不過,在 150MHz,放大器具有 305° 相位滯后和 5dB 增益。輸出極點具有一個相位

–atan(150MHz/106MHz) = –55°

和一個增益

循環(huán)地倍增增益,我們獲得 360° 相位和 +0.2dB 增益,又是一個振蕩器。50pF 似乎是將強制 LTC6268 產(chǎn)生振蕩的最小負載電容。

防止負載電容引起振蕩的最常見方式是,在反饋連接之后,簡單地給電容串聯(lián)一個小阻值的電阻器。10Ω 至 50Ω 的阻值將限制容性負載可能引起的相位滯后,并在速度非常高的時候,隔離放大器和低容性阻抗。缺點包括隨負載電阻特性而變化的 DC 和低頻誤差、容性負載頻率響應受到限制、以及如果負載電容在電壓變化時不恒定所導致的信號失真。

提高放大器的閉環(huán)增益,常??梢苑乐关撦d電容引起的振蕩。以較高的閉環(huán)增益運行放大器意味著,在環(huán)路相位為 ±360° 的頻率上,反饋衰減器也衰減環(huán)路增益。例如,如果我們使用 LTC6268 時,其閉環(huán)增益為 +10,那么我們會看到,放大器在 40MHz 時有 10V/V 或 20dB 增益,相位滯后 285°。要激起振蕩,就需要一個輸出極點,導致額外的 75° 滯后。通過 –75° = –atan(40MHz/Fpole) → Fpole = 10.6MHz,我們可以求出輸出極點。這個極點頻率來自 500pF 負載電容和大小為 30 的輸出阻抗。輸出極點增益為

由于未加載的開環(huán)增益為 10,所以我們得到,振蕩頻率上的繞環(huán)路增益為 0.26,因此這一次我們不會產(chǎn)生振蕩,至少不會產(chǎn)生由一個簡單的輸出極點引起的振蕩。這樣,通過提高閉環(huán)增益,我們將負載電容容限從 50pF 提高到了 500pF。

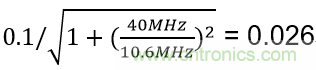

另外,無端接的傳輸線也是非常糟糕的負載,因為它們會帶來隨頻率而重復的“失控式”阻抗和相位變化 (見圖 7 中一根無端接 9 英尺電纜的阻抗)。

圖7:未端接同軸電纜的阻抗和相位

如果您的放大器能夠在某種低頻諧振條件下安全地驅(qū)動電纜,那么它很可能在某個較高的頻率振蕩,這是因為其自己的相位裕度減少了。如果電纜必須是無端接的,則一個與輸出端相串聯(lián)的“背匹配”(back-match) 電阻器能夠隔離電纜的極端阻抗變化。此外,即使來自電纜未端接端的瞬態(tài)反射正好反沖回放大器,如果向后匹配電阻器的阻值與電纜特性阻抗相匹配,那么該電阻器也能恰當?shù)匚者@種能量。如果向后匹配電阻器與電纜阻抗不匹配,那么有些能量就會從放大器和端子反射,一路回到未端接端。當能量到達該端時,再次迅速反射回放大器,結(jié)果,就有了一系列來回跳動的脈沖,但每次都有衰減。

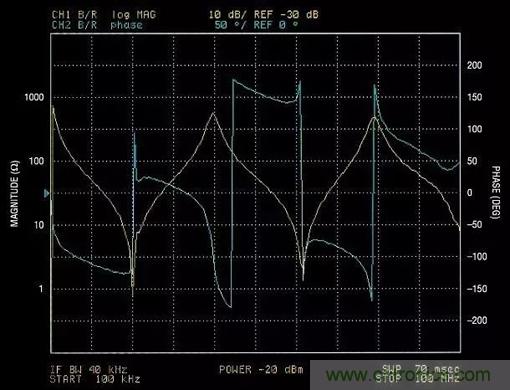

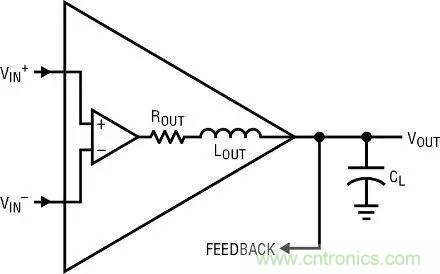

圖 8 顯示了一個更完整的輸出阻抗模型。ROUT 項與我們在 LTC6268 中討論過的一樣,也是 30Ω,這里又增加了一個 Lout 項。這是一個物理電感和電子等效電感的組合。物理封裝、接合線和外部電感加起來為 5nH 至 15nH,封裝越小,這個數(shù)值就越小。

圖8:放大器輸出阻抗的電感性組件

此外,任何放大器都有 20nH 至 70nH 的電生電感,尤其是雙極型器件。器件的有限 Ft 將輸出晶體管的寄生基極電阻變成電感。危害是,Lout 與 CL 可能相互作用,形成一個串聯(lián)諧振電路,那么同樣的問題又來了,如果環(huán)路中沒有更大的相位滯后,串聯(lián)諧振電路的阻抗就可能降至 Rout 無法驅(qū)動的水平,從而可能產(chǎn)生振蕩。例如,設定 Lout = 60nH 和 CL = 50pF。諧振頻率

剛好位于 LTC6268 通帶內(nèi)。實際上,這個串聯(lián)諧振電路在諧振時加載到了輸出端,嚴重改變了諧振頻率附近的環(huán)路相位。不幸的是,Lout 在放大器的數(shù)據(jù)表中并不提及,但有時可以在開環(huán)輸出阻抗圖上看到它的影響??傊?,對帶寬小于 50MHz 左右的放大器而言,這種影響并不重要。

一種解決方案如圖 9 所示。Rsnub 和 Csnub 形成了所謂的“減震器”,其目的是降低諧振電路的 Q 值,這樣諧振電路就不會在放大器輸出端加上很低的諧振阻抗。Rsnub 的值通常估定為諧振時 CL 的電抗 (本例中為 -j35Ω),以將輸出諧振電路的 Q 值降至 1 左右。調(diào)整 Csnub 的大小,以將 Rsnub 完全插入輸出諧振頻率處,即 Csnub 的電抗 <

圖9:使用一個輸出減震器

電流反饋放大器的負輸入實際上是一個緩沖器輸出,也將展現(xiàn)圖 8 所示的一系列特點。因此,該輸入就像一個輸出一樣,可能靠著 Cpar 產(chǎn)生自振蕩。Cpar 和任何有關(guān)的電感都必須最大限度減小。不幸的是,減震器在負輸入端會隨著頻率變化改變閉環(huán)增益,因此不實用。

奇怪的阻抗

很多放大器在高頻時輸入阻抗都有點反常。有兩個串聯(lián)輸入晶體管的放大器最是如此,如達林頓 (Darlington) 配置。很多放大器在輸入端都有 npn/pnp 晶體管對,其行為表現(xiàn)隨頻率的變化與達林頓配置類似。輸入阻抗的實數(shù)部分在有些頻率 (一般遠高于 GBF) 上會變成負的。電感性源阻抗會與輸入和電路板電容諧振,負的實數(shù)分量可能激起振蕩。當用未端接電纜驅(qū)動時,這還有可能導致在很多重復頻率上的振蕩。如果輸入端不可避免地使用長的電感性導線,那么可用幾個串聯(lián)的、可以吸收能量的電阻器斷開導線,或者可以在放大器輸入引線上安裝一個阻抗為中等大小的減震器 (約 300Ω)。

電源

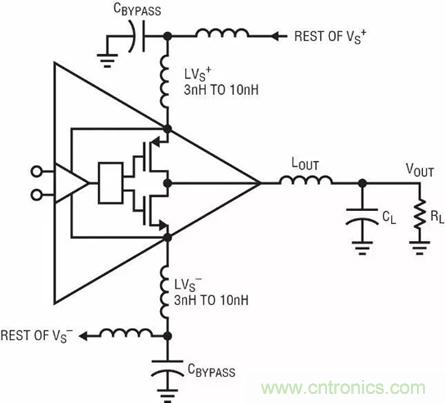

最后一個需要考慮的振蕩源是電源旁路。圖 10 顯示了輸出電路的一部分。LVS+ 和 LVS– 是不可避免的封裝、IC 接合線、旁路電容器的物理長度 (像任何導體一樣也是電感性的) 以及電路板走線的串聯(lián)電感。還包括將局部旁路組件連接到電源總線其余部分 (如果不是電源平面) 的外部電感。盡管 3nH 至 10nH 看起來似乎不大,但是在 200MHz 時,就是 3.8 至 j12Ω。如果輸出晶體管傳導大的高頻輸出電流,那么在電源電感兩端會存在壓降。

圖10:電源旁路細節(jié)

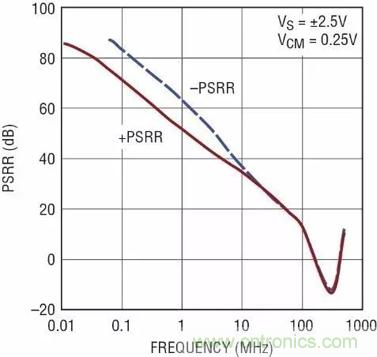

放大器的其余部分需要無噪聲電源,因為這些部分不能隨著頻率變化抑制電源噪聲。在圖 11 中我們可以看到 LTC6268 隨頻率變化的電源抑制比 (PSRR)。在所有運算放大器中,因為沒有接地引腳,所以補償電容器都連接到電源,會將電源噪聲耦合到放大器中,gm 必須抵消這種噪聲。由于補償,PSRR 隨著 1/f 降低,而且過了 130MHz 后,電源抑制實際上在變大。在 200MHz 時,因為 PSRR 的增大,輸出電流可能干擾 LVs 電感器內(nèi)部的電源電壓,通過 PSRR 的放大,干擾變成很強的放大器信號,驅(qū)動輸出電流、產(chǎn)生內(nèi)部電源信號等,導致放大器振蕩。這就是所有放大器的電源都必須用電感很小的走線和組件精心旁路的原因。此外,電源旁路電容器必須比任何負載電容都大得多。

圖11:LTC6268隨頻率變化的電源抑制

如果我們考慮 500MHz 左右的頻率,那么 3nH 至 10nH 就變成 j9.4Ω 至 j31.4Ω 了。這已經(jīng)足夠輸出晶體管靠其電感和 IC 組件電容產(chǎn)生自振蕩了,尤其是在輸出電流較大 (晶體管 gm 和帶寬增大) 時。因為用如今的半導體制造工藝生產(chǎn)的晶體管帶寬很大,所以需要特別注意,至少在大輸出電流時。

結(jié) 論

總之,設計師需要考慮與每個運算放大器端子有關(guān)的寄生電容和電感以及負載的性質(zhì)。放大器被設計成在標稱環(huán)境中是穩(wěn)定的,但是每種應用都需要針對其自身的分析。

推薦閱讀: