【導讀】每個PWM DAC設計都需要模擬濾波,以便將需要的直流分量(與 PWM占空比成正比)與不需要的交流紋波分開。選擇足夠大的RC乘積可以實現(xiàn)任何期望的紋波衰減,但是穩(wěn)定時間會受到影響。對許多應用而言,需在電路復雜度與PWM DAC性能之間進行合理折衷。

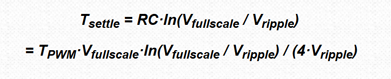

每個PWM DAC設計都需要模擬濾波,以將需要的直流分量(與PWM占空比成比例)與不需要的交流紋波分開。最簡單的方法是采用基本的RC低通濾波器,它給出峰峰值紋波幅度(這是針對50%PWM占空比的最壞情況,其中TPWM=PWM周期時間,并假設RC>TPWM):

顯而易見的設計取舍是:雖然選擇足夠大的RC乘積可以實現(xiàn)任何期望的紋波衰減度,但是穩(wěn)定時間將相應地受到影響。例如,如果我們(相當邏輯地)選擇穩(wěn)定帶等于紋波幅度這樣一種定義,則:

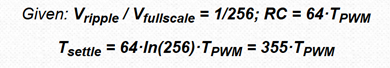

這種關系的結果可以用8位的例子來說明:

這里,即使有相當快的32kHz(31µs TPWM),穩(wěn)定時間仍然是相當冗長的11ms。

顯然,如果穩(wěn)定時間是個關鍵的設計參數(shù),我們就需要做得更好,并找到一個不會過于簡單的濾波方案。我以前寫的一篇設計實例“快速穩(wěn)定的同步PWM-DAC濾波器幾乎沒有紋波”說明了沿這個思路的極大可能性。

但并不是每個應用都不能容忍冗長的355TPWM穩(wěn)定時間或可證明確實需要這樣一種復雜的濾波方案。本設計實例解決了這些常見的應用問題。如圖1所示,它通過一個反相器、R2和C2對基本的R1/C1低通濾波器進行了增強;反相器、R2和C2一道從所需的直流信號中抵沖并減去(大部分)不需要的交流分量,從而得到一個相對干凈的模擬信號輸出,其穩(wěn)定時間比簡單的RC濾波器短得多。

圖1:PWM DAC紋波消除器的波形和原理圖。

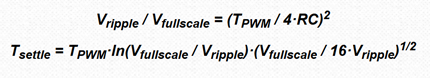

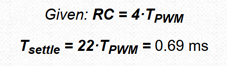

但是,“相對干凈”是多干凈?“快得多”又是多快?設置R2=R1和C2=C1,則新電路的紋波和穩(wěn)定時間值為:

再次參考8位的例子(見圖1):

采用32kHz的周期,速度提高了16倍,紋波-幅度比成倍提高!

對許多應用而言,這是在電路復雜性的適度增加和PWM DAC性能的顯著提高之間非常有價值的折衷。

本文轉(zhuǎn)載自電子技術設計。

推薦閱讀: