【導讀】看完《高速設計的三座大山——串聯(lián)電阻對信號的影響》的小伙伴們,有木有發(fā)現(xiàn)匹配最好的串聯(lián)端接電阻的阻值不是50ohm,而是30ohm。這是為什么呢?

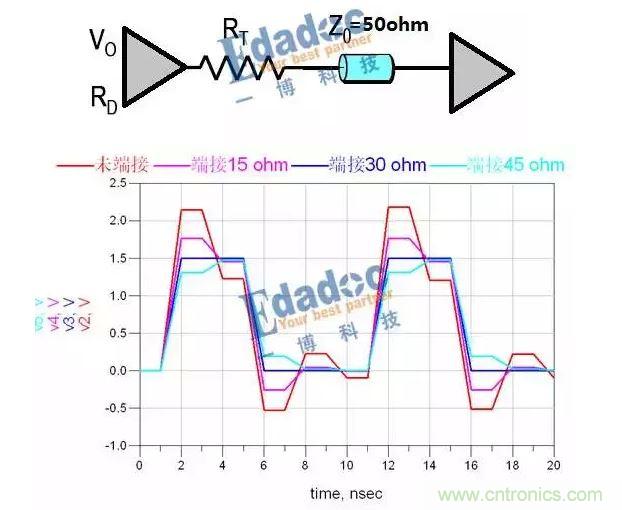

看完(2)的小伙伴們,有木有發(fā)現(xiàn)匹配最好的串聯(lián)端接電阻的阻值不是50ohm,而是30ohm,如下圖。這是為什么呢?

對高速數(shù)字電路設計有一定了解的人就知道,其實驅動器本身有內(nèi)阻,做串聯(lián)端接匹配時,串聯(lián)電阻的阻值和驅動內(nèi)阻加起來大致等于傳輸線阻抗就可以了,即R_D+R_T≈Z_0 。

這個時候,有童鞋可能就要跳起來了,MR''S,你說的倒是容易,我也知道驅動內(nèi)阻R_D 加串聯(lián)電阻等于傳輸線阻抗這個公式,大家都知道,so easy啊,問題在于,傳輸線阻抗可以很輕松的在datasheet找到,可是驅動器內(nèi)阻上哪兒去找, datasheet上又沒有?

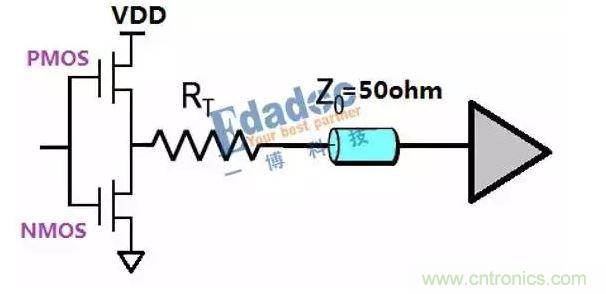

下圖是一個簡單的驅動電路。

當驅動器持續(xù)輸出高電平時,PMOS管導通,NMOS關閉,電流流經(jīng)PMOS輸出,這個時候電流感受到的驅動內(nèi)阻RD是PMOS管的導通電阻R_P;反之,當電流持續(xù)輸出低電平時,電流感受到的驅動內(nèi)阻RD就是NMOS管的導通電阻RN 。一般情況下,PMOS管的導通電阻R_P 比NMOS管的導通電阻R_N 要大,這是它們的工藝所決定的,從上一篇(2)中,我們可以知道,輸出高電平時,其RC時間常數(shù)會大,上升沿更緩。有時候,我們看到信號的上升沿比下降沿要更緩一些,就是這個原因啦。

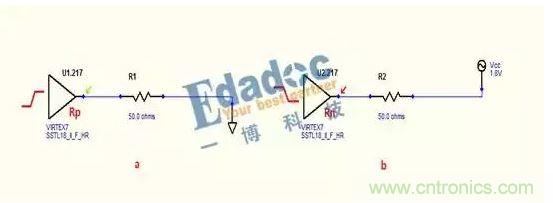

下面,我們來看一下怎樣得到驅動內(nèi)阻的阻值?先使用仿真工具搭建兩個簡單的電路,如下:

以Xilinx V7芯片DDR2驅動為例,在圖a的驅動端中加入上升沿驅動(PMOS導通),通過50ohm電阻下拉到地,通過電阻分壓的原理,即V_meas=50/(50+R_P )×VCC,可以求的R_P的值。

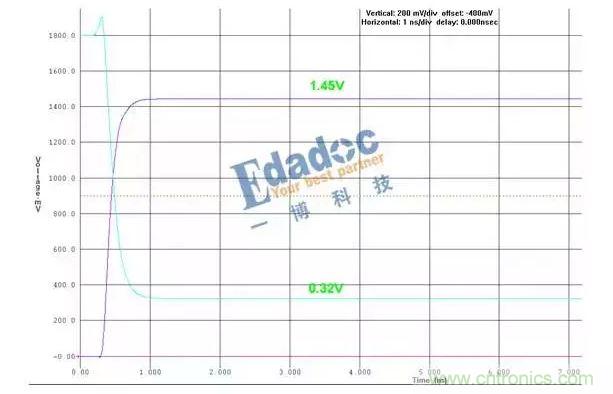

在圖b中驅動端加入下降沿驅動(NMOS導通),通過50ohm電阻上拉到VCC,通過電阻分壓的原理,即V_meas=R_N/(50+R_N )×VCC,可以求得R_N的值。下圖是仿真得到的波形:

通過計算可以得到,R_P=12.1 ohm,R_N=10.8 ohm,兩個阻抗值相差不大,選取任何一個值來計算端接電阻,都可以。通過這樣簡單的仿真,我們就可以獲得驅動器的驅動內(nèi)阻啦。

有時候,我們還會遇到這兩個值差別比較大的情況,比如R_P=20ohm,R_N=10ohm,那這個時候我們要怎么選擇呢?如果選擇R_P來計算匹配電阻,則匹配電阻R_T=30 ohm,高電平匹配很好,低電平時,匹配電阻就偏小,信號傳輸?shù)絺鬏斁€端時會出現(xiàn)正反射,過沖較大;如果選擇R_N來計算匹配電阻,則R_T=40ohm,低電平匹配很好,高電平時,匹配電阻就偏大,信號傳輸?shù)絺鬏斁€時出現(xiàn)負反射,上升沿會出現(xiàn)臺階,另外,上升沿還會因為R_T的增大而變緩。所以,這兩種選擇有利有弊,遇到這種情況時,就需要設計者酌(zi)情(qiu)考(duo)量(fu)啦。

不過我可以給大家泄露一個天機,假如你遇到了這種情況,你可以悄悄的來找高速先生幫你評估。