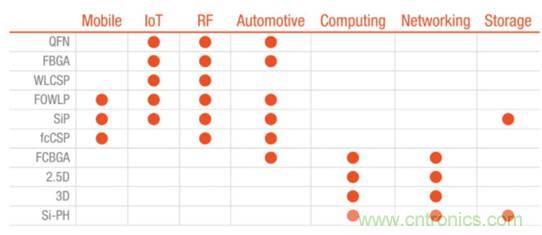

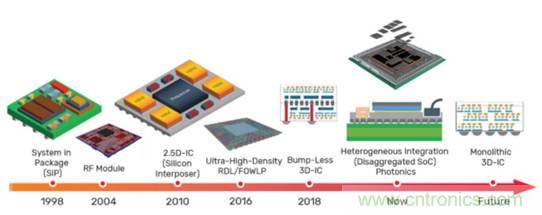

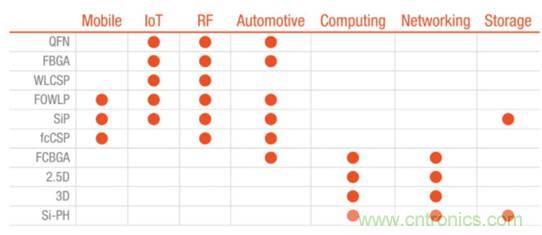

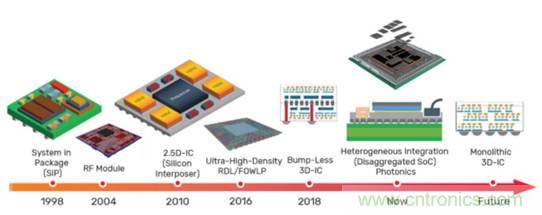

將多個(gè)芯片封裝在一起的選項(xiàng)包括系統(tǒng)級封裝、多芯片模塊�、芯片級、小芯片���、異構(gòu)����、2.5D 和 3D 堆疊等。正在開發(fā)的多芯片量子處理器可以解決容錯(cuò)量子計(jì)算機(jī)的關(guān)鍵擴(kuò)展挑戰(zhàn)�����。共同封裝光學(xué)器件 (CPO) 或封裝光學(xué)器件 (IPO) 正在出現(xiàn)�����,它們將光學(xué)器件和開關(guān)硅集成在同一封裝中���,從而在曾經(jīng)不相交和獨(dú)立的技術(shù)之間產(chǎn)生協(xié)同作用,并節(jié)省大量功率��。

多芯片封裝技術(shù)的演進(jìn)�����。(圖片:Cadence 設(shè)計(jì)系統(tǒng))

小芯片��、MCM 和 SiP

基于小芯片(Chiplet)的設(shè)計(jì)�、多芯片模塊 (MCM) 和系統(tǒng)級封裝 (SiP) 是或可以是異構(gòu)集成的形式��,在定義這三種封裝風(fēng)格時(shí)存在非常大的灰色區(qū)域��。一家公司的基于小芯片的設(shè)計(jì)可能被另一家供應(yīng)商稱為 MCM���,而 MCM 和 SiP 通常被歸為同一類別。下面回顧了一些細(xì)微差別����。

小芯片是經(jīng)過測試的 IP 功能的物理實(shí)現(xiàn),具有在硅晶片上制造的標(biāo)準(zhǔn)通信接口��,可通過提高制造產(chǎn)量和跨應(yīng)用程序的可重用性來降低成本��。給定解決方案中的小芯片可以具有不同的工藝節(jié)點(diǎn)��。小芯片提供標(biāo)準(zhǔn)功能���,使設(shè)計(jì)人員能夠?qū)W⒂谠O(shè)計(jì)中的獨(dú)特 IP��。結(jié)果被稱為“偽 SoC”�,其設(shè)計(jì)速度比完全集成的 SoC 解決方案更快����、成本更低�����?��;谛⌒酒慕鉀Q方案通常不包括無源設(shè)備或其他“非硅”設(shè)備。小芯片解決方案的一個(gè)例子可以是當(dāng)今的一些微處理器����,其中處理器內(nèi)核和 I/O 駐留在通用封裝中的不同硅芯片上。

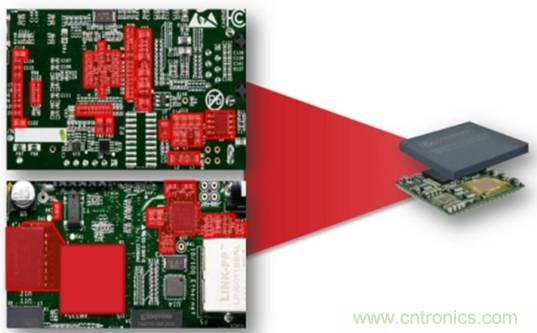

MCM 最初僅集成多個(gè)芯片����,不包括無源器件或其他組件���。 MCM 中的芯片是“完整”的 IC����,例如處理器�、GPU 和 RF 部分,而不是更簡單的單功能小芯片�。隨著概念的發(fā)展,MCM 的尺寸越來越大并集成了額外的組件����,于是 SiP 誕生了���。 MCM 和 SiP 之間的主要區(qū)別在于 MCM 不必是一個(gè)完整的系統(tǒng)。根據(jù)定義�����,SiP 是單個(gè)封裝中的系統(tǒng)���。

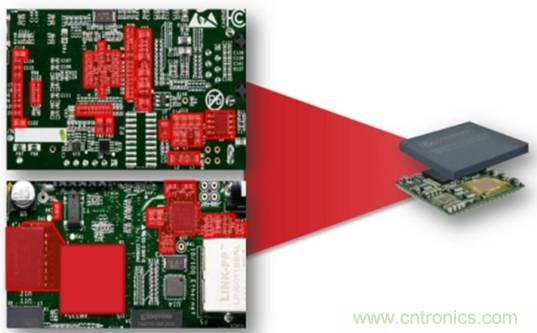

MCM 是封裝中緊密耦合的子系統(tǒng)或模塊�。 SiP將多個(gè) IC 以及支持的無源器件集成到單個(gè)封裝中��。與 MCM 一樣���,SiP 可以使用來自最佳單個(gè)工藝或工藝節(jié)點(diǎn)的硅來優(yōu)化性能并實(shí)現(xiàn)所需的集成�����。SiP 被設(shè)計(jì)為一個(gè)完整的系統(tǒng)并用作單個(gè)組件����。

系統(tǒng)級封裝 (SiP),有時(shí)稱為多芯片模塊 (MCM)�����,將多個(gè) IC 和無源器件集成到單個(gè)封裝中��。 (圖片:Octavo 系統(tǒng))

2.5D 和 3D 封裝

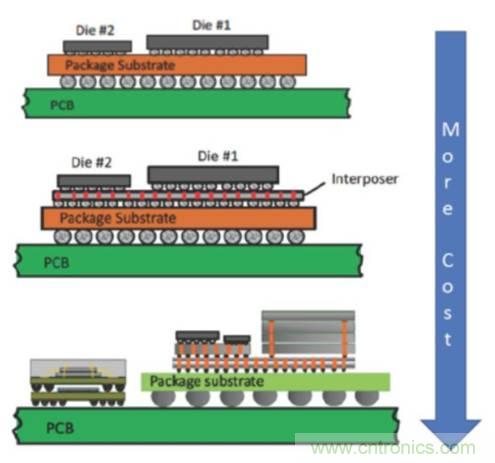

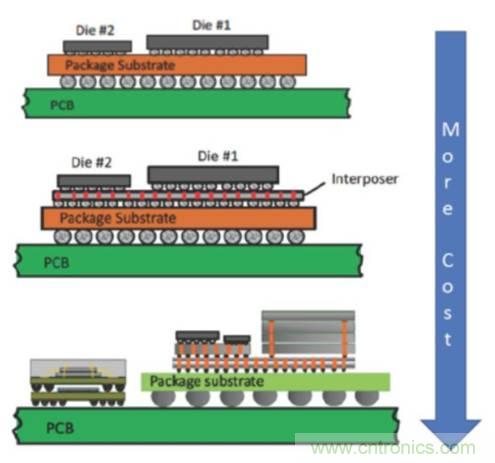

使用硅通孔 (TSV) 互連多個(gè)管芯通常被認(rèn)為是 MCM 或 SiP 與 2.5D 封裝器件之間的區(qū)別��。 TSV 為 MCM 和 SiP 中的有機(jī)基板提供了高密度替代品���。使用 TSV 可以獲得 3D 封裝的一些好處��,而沒有與全 3D 方法相關(guān)的挑戰(zhàn)和成本���。簡而言之,與傳統(tǒng)的 MCM 或 SiP 解決方案相比�,將多個(gè)管芯放置在具有非常細(xì)間距 TSV 的中介層上會產(chǎn)生互連和更好的重量�����、尺寸和功率特性��。

全3D IC則是更進(jìn)一步����,使用 TSV 在垂直維度上堆疊�����。它可以產(chǎn)生更小和更高性能的解決方案����。 3D 封裝是另一種形式的垂直集成�,指的是使用引線鍵合和倒裝芯片等互連方法進(jìn)行 3D 集成。 3D 封裝可分為 3D 系統(tǒng)級封裝 (3D SiP)�����、3D 晶圓級封裝 (3D WLP) 和 3D 層疊封裝 (3D PoP)�����。與 2.5D 封裝相比�����,各種形式的 3D 封裝都有一些缺點(diǎn)����,包括:

通過將芯片并排放置而不是垂直堆疊可以提高散熱性能�����。

3D 結(jié)構(gòu)本質(zhì)上更復(fù)雜����,修改或升級 2.5D 裝配通常更簡單����、更快。升級 2.5D 器件就像使用新的中介層或用改進(jìn)版本替換一個(gè)或多個(gè)芯片一樣簡單���。

2D 封裝在封裝基板上的單個(gè)平面上安裝 2 個(gè)或更多裸片�,2.5D 在裸片和封裝基板之間添加一個(gè)中介層�,3D 堆疊則是在垂直維度進(jìn)行集成。 (圖片:美國宇航局)

晶圓級和芯片級

使用晶圓級封裝 (WLP)�����,晶圓制造工藝擴(kuò)展到包括晶圓切割之前的器件互連�����。大多數(shù)其他封裝首先進(jìn)行晶圓切割�����,然后將單個(gè)管芯放入塑料封裝中并連接焊料凸點(diǎn)���。 WLP 在切割晶圓之前將封裝的底部和頂部輸出層以及焊料凸塊連接到 IC��。由于封裝與裸片的尺寸基本相同���,因此 WLP 是芯片級封裝 (CSP) 技術(shù)的一種形式。

WLP 用于需要盡可能最小的解決方案的應(yīng)用�,例如智能手機(jī)。然而��,WLP 的局限性在于��,由于封裝尺寸非常小�,可以支持的觸點(diǎn)數(shù)量有限。在高度復(fù)雜和緊湊的系統(tǒng)中���,扇出晶圓級封裝 (FO-WLP) 增強(qiáng)了標(biāo)準(zhǔn) WLP 以克服有限的 I/O 功能��。

與傳統(tǒng)封裝相比����,F(xiàn)O-WLP 可實(shí)現(xiàn)更小的封裝尺寸以及改進(jìn)的散熱和電氣性能。盡管如此���,F(xiàn)O-WLP 還是比 WLP 大����,而且 FO-WLP 支持更多數(shù)量的觸點(diǎn)����,但不會增加芯片尺寸。在 FO-WLP 中����,首先切割晶圓,然后將芯片精確地重新定位在載體晶圓上���,每個(gè)芯片周圍都有一個(gè)扇出區(qū)域���。模具成型,然后添加焊球�����。

光學(xué)封裝

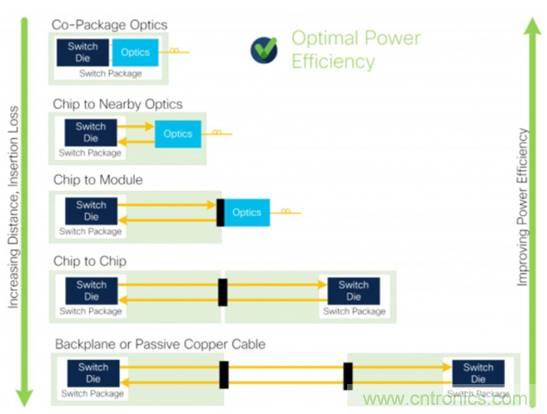

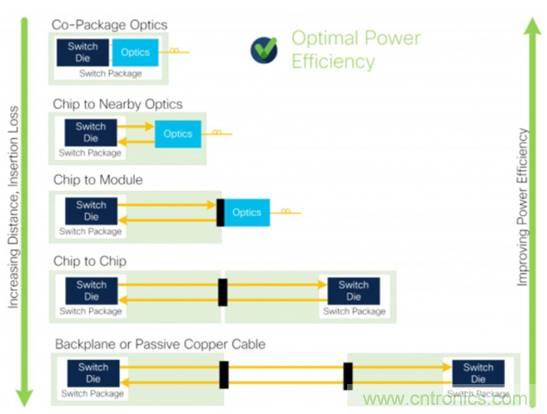

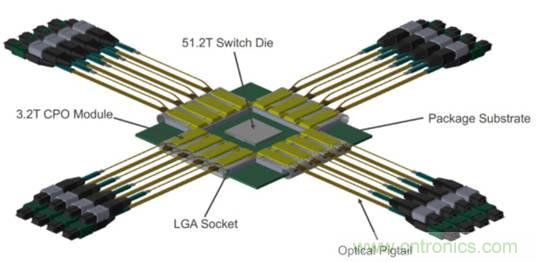

高速數(shù)字網(wǎng)絡(luò)(例如超大規(guī)模數(shù)據(jù)中心)中的序列化-反序列化 (SerDes) 功能通常涉及基于硅的通信鏈路和基于光的鏈路之間的接口�����。隨著光學(xué)引擎和開關(guān)硅之間的距離減小�,通道插入損耗也隨之下降,從而節(jié)省了大量功率����。最接近的間距是通過共同封裝光學(xué)器件 (CPO) 實(shí)現(xiàn)的,其中接口的兩側(cè)都在一個(gè)封裝中�����。

共同封裝的光學(xué)器件具有最短的互連距離和最大的節(jié)能效果�。 (圖片:思科系統(tǒng))

正在開發(fā) CPO 的兩項(xiàng)工作是車載光學(xué)聯(lián)盟 (COBO) 和共同封裝光學(xué)聯(lián)合開發(fā)基金會 (CPO JDF)。COBO 已經(jīng)創(chuàng)建了一個(gè) CPO 工作組��,專注于為 CPO 實(shí)施制定技術(shù)指南和標(biāo)準(zhǔn)�。它由對在超大規(guī)模數(shù)據(jù)中心使用 CPO 感興趣的最終用戶和技術(shù)供應(yīng)商組成。COBO 活動主要對 CPO 實(shí)施所需的遠(yuǎn)程激光源和光學(xué)連接感興趣����,預(yù)計(jì)它將與其他 CPO 標(biāo)準(zhǔn)化活動相輔相成。

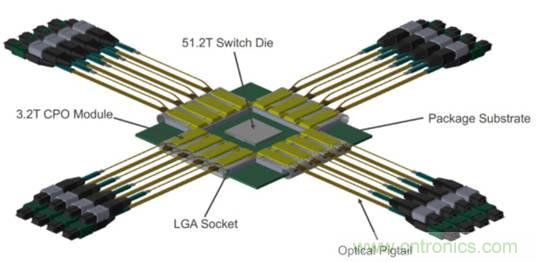

Facebook 和微軟成立了CPO JDF��,其主要考慮與 CPO 相關(guān)的系統(tǒng)集成問題有關(guān)���。 CPO JDF 發(fā)布了一份產(chǎn)品需求文檔 (PRD)���,描述了旨在提高網(wǎng)絡(luò)交換機(jī)密度和電源效率的 8x400G CPO 模塊����。 PRD 要求使用 XSR(極短距離)接口��。 XSR 針對封裝基板上的芯片到光學(xué)引擎 (D2OE) 接口和芯片到芯片 (D2D) 接口進(jìn)行了優(yōu)化���,最大可達(dá)約 100 毫米 × 100 毫米�����。

基于XSR接口規(guī)范的3.2T CPO模塊組裝���。 (圖片:車載光學(xué)聯(lián)盟)

16 個(gè) XSR CPO 模塊將用于構(gòu)建低功耗 51.2Tb/s 交換機(jī)。 PRD 定義了 CPO 模塊的兩種變體�,一種支持 400GBASE-FR4(8 個(gè) Tx/Rx 光纖對),一種支持 400GBASE-DR4(總共 32 個(gè) Tx/Rx 光纖對)��。

多芯片量子處理器

擴(kuò)展量子計(jì)算機(jī)具有挑戰(zhàn)性�����。隨著量子處理器尺寸的增加,制造良率下降����。實(shí)現(xiàn)糾錯(cuò)量子計(jì)算需要大量的量子位(qubit)��。正在努力將多個(gè)較小的芯片連接到一個(gè)大規(guī)模的量子處理器中��。這種多芯片方法有望簡化大型量子處理器的創(chuàng)建�����,并支持該技術(shù)的可預(yù)測和加速擴(kuò)展����。

縮放是開發(fā)容錯(cuò)量子計(jì)算機(jī)的關(guān)鍵。預(yù)計(jì)今年晚些時(shí)候?qū)y試一個(gè) 80 量子位的系統(tǒng)���。將多芯片模塊技術(shù)應(yīng)用于量子處理器可以產(chǎn)生足夠大的系統(tǒng)來運(yùn)行實(shí)際應(yīng)用�����,包括所需的糾錯(cuò)����。

多芯片量子處理器。 (圖片:Rigetti Computing)

概括

數(shù)字 IC�、光互連和量子處理器的封裝選擇越來越多。先進(jìn)的封裝技術(shù)支持異構(gòu)集成以及使用來自最佳單個(gè)工藝或工藝節(jié)點(diǎn)的 IC 來優(yōu)化性能并實(shí)現(xiàn)所需的集成��。持續(xù)的封裝開發(fā)對于實(shí)現(xiàn)從手機(jī)到超大規(guī)模數(shù)據(jù)中心的先進(jìn)系統(tǒng)解決方案非常重要�����。