【導(dǎo)讀】數(shù)字電位計(jì) (digiPOTs)通常用于方便的調(diào)整傳感器的交流或直流電壓或電流輸出��、電源供電�、或其他需要某種類型校準(zhǔn)的器件���,比如定時(shí)、頻率��、對比度、亮度���、增益��,以及失調(diào)調(diào)整���。數(shù)字設(shè)置幾乎可以避免機(jī)械電位計(jì)相關(guān)的所有問題,比如物理尺寸����、機(jī)械磨損��、游標(biāo)調(diào)定�、電阻漂移,以及對振動�、溫度和濕度敏感等問題��,還可以消除因使用螺絲刀導(dǎo)致的布局不靈活問題����。

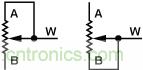

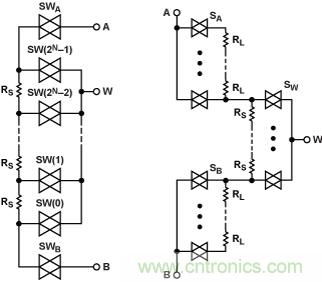

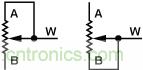

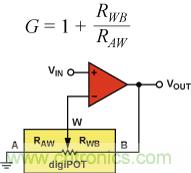

digiPOT有兩種使用模式����,即電位計(jì)模式或可變電阻器模式�����。圖1所示為電位計(jì)模式�����,此時(shí)有3個端子��,信號通過A端和B端連接���,W端(類似游標(biāo))則提供衰減的輸出電壓��。當(dāng)數(shù)字比率控制輸入為全零時(shí)�,游標(biāo)通常與B端連接����。

圖1.電位計(jì)模式

游標(biāo)硬連線至任一端時(shí),電位計(jì)就變成了簡單的可變電阻器, 如圖2所示���?�?勺冸娮杵髂J綍r(shí)需要的外部引腳更少�,因此尺寸更小���。部分digiPOT只有可變電阻器模式�����。

圖2.可變電阻器模式

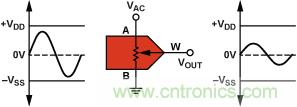

digiPOT電阻端的電流或電壓極性沒有限制��,但是交流信號的幅度不能超過電源供電軌(VDD 和 VSS)器件在可變電阻器模式��,尤其是低電阻設(shè)置狀態(tài)下工作時(shí)��,最大電流或電流密度, 應(yīng)加以限制.

典型應(yīng)用

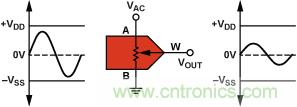

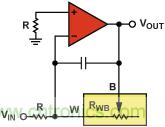

信號衰減是電位計(jì)模式的固有特性��,因?yàn)樵撈骷举|(zhì)上屬于分壓器��。輸出信號定義為: VOUT = VIN × (RDAC/RPOT), 其中RPOT是digiPOT的標(biāo)稱端對端電阻���,RDAC 是通過數(shù)字方式選擇的W端和輸入信號參考引腳之間的電阻,參考引腳通常為B端�����,如圖3所示.

圖3.信號衰減器

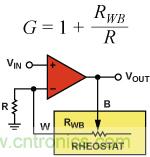

信號放大需要有源器件,通常是反相或同相放大器�����。通過適當(dāng)?shù)脑鲆婀?�,電位?jì)模式或可變電阻器模式均可使用

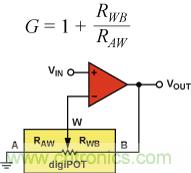

圖4顯示的是同相放大器���,此時(shí)digiPOT相當(dāng)于電位計(jì)�����,可通過反饋調(diào)整增益����。由于部分輸出會反饋, RAW/(RWB + RAW),應(yīng)等于輸入�����,理想增益為:

圖4.電位計(jì)模式中的同相放大器

該電路的增益與RAW, 成反比RAW接近零時(shí)會迅速上升���,顯示出雙曲線傳遞函數(shù)特性�����。為了限制最大增益�,可插入一個電阻與RAW(位于增益公式的分母內(nèi))串聯(lián)

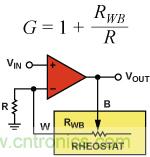

如果需要線性增益關(guān)系,可以采用可變電阻器模式以及固定外部電阻��,如圖5所示���,增益現(xiàn)定義如下:

圖5.可變電阻器模式中的同相放大器

將低電容端(最新器件中為W引腳)連接至運(yùn)算放大器輸入可獲得最佳性能.

digiPOT用于信號放大的優(yōu)勢

圖4和圖5所示的電路具有高輸入阻抗和低輸出阻抗,可工作于單極性和雙極性信號��。digiPOT可用于游標(biāo)操作���,采用固定外部電阻在更小的范圍內(nèi)提供更高的分辨率��,還可用于運(yùn)算放大器電路���,信號有無反轉(zhuǎn)均可。此外�,digiPOT的溫度系數(shù)較低,電位計(jì)模式時(shí)通常為5 ppm/°C�����,可變電阻器模式時(shí)則為35 ppm/°C。

digiPOT用于信號放大的限制

處理交流信號時(shí)���,digiPOT的性能受帶寬和失真的限制��。受寄生器件影響��,帶寬是指在小于3 dB衰減時(shí)能夠通過digiPOT的最大頻率�����?��?傊C波失真 (THD)(此處定義為后四個諧波的rms之和與輸出基波值的比值)是信號通過器件時(shí)衰減的量度。這些規(guī)格涉及的性能限制由內(nèi)部digiPOT架構(gòu)決定�。通過分析,我們可以更好地全面了解這些規(guī)格�����,減少其負(fù)面

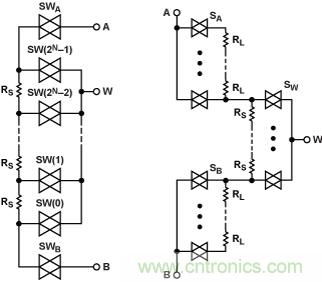

內(nèi)部架構(gòu)已從傳統(tǒng)的串聯(lián)電阻陣列(如圖6a所示)發(fā)展至分段式架構(gòu)(如圖6b所示)����。主要的改進(jìn)是減少了所需內(nèi)部開關(guān)的數(shù)量。第一種情況采用串行拓?fù)浣Y(jié)構(gòu)�,開關(guān)數(shù)量為N = 2n是分辨率的位數(shù)��。n = 10,時(shí)���,需要1024個開關(guān)

圖6. a)傳統(tǒng)架構(gòu),b)分段式架構(gòu)

專有(專利)分段式架構(gòu)采用級聯(lián)連接��,可以最大限度地減少開關(guān)總數(shù)���。圖6b的例子顯示的是兩段式架構(gòu),由兩種類型的模塊組成����,即左側(cè)的MSB和右側(cè)的LSB。

左側(cè)上下模塊是一串用于粗調(diào)位數(shù)的開關(guān)(MSB段)���。右側(cè)模塊是一串用于精調(diào)位數(shù)的開關(guān)(LSB段)�����。MSB開關(guān)粗調(diào)后接近RA/RB比�����。LSB串的總電阻等于MSB串中的單個阻性元件�����,LSB開關(guān)可對主開關(guān)串上的任一點(diǎn)進(jìn)行比率精調(diào)��。A和B MSB開關(guān)為互補(bǔ)碼����。

分段式架構(gòu)的開關(guān)數(shù)量為:

N = 2m + 1 + 2n – m,

其中n是總位數(shù),m是MSB字的分辨率位數(shù)���。例如n = 10 and m = 5, 則需要96個開關(guān)�。

分段式方案需要的開關(guān)數(shù)少于傳統(tǒng)開關(guān)串:

兩者相差的開關(guān)數(shù) = 2n – (2m + 1 + 2n – m)

在該例中����,節(jié)省的數(shù)量為

1024 – 96 = 928!

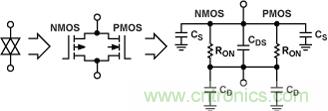

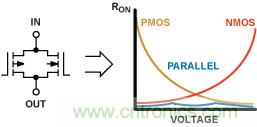

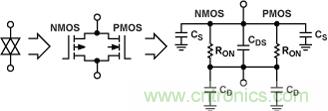

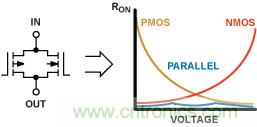

兩種架構(gòu)都必須選擇不同電阻值的開關(guān),充分考慮到模擬開關(guān)中的交流誤差源�。這些CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)開關(guān)由并行P溝道和N溝道MOSFET構(gòu)成。這種基本雙向開關(guān)可以保持相當(dāng)恒定的電阻(RON) 信號可達(dá)完整的供電軌.

帶寬

圖7顯示的是影響CMOS開關(guān)交流性能的寄生器件���。

圖7.CMOS開關(guān)模式

CDS = 漏極-源級電容; CD = 漏極-柵級 + 漏極-體電容;CS = 源級-柵級 + 源級-體電容.

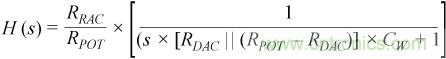

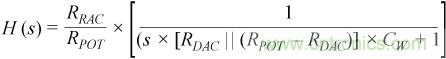

傳遞關(guān)系如以下公式定義����,其中包含的假設(shè)為:

● 源阻抗為 0 ?

● 無外部負(fù)載影響

● 無來自CDS的影響

● RLSB << RMSB

其中:

RDAC是設(shè)定電阻

RPOT是端對端電阻

CDLSB是LSB段的總漏極-柵級 + 漏極-體電容

CSLSB是LSB段的總源級-柵級 + 源級-體電容

CDMSB是MSB開關(guān)的漏極-柵級 + 漏極-體電容

CSMSB是MSB開關(guān)的源級-柵級 + 源級-體電容

moff是信號MSB路徑的斷開開關(guān)數(shù)量

mon是信號MSB路徑的接通開關(guān)數(shù)量

傳遞公式受各種因素影響,與代碼存在一定關(guān)聯(lián)��,因此我們采用以下額外假設(shè)來簡化公式

CDMSB + CSMSB = CDSMSB

CDLSB + CSLSB >> CDSMSB

(CDLSB + CSLSB) = CW (詳見數(shù)據(jù)手冊)

CDS對傳遞公式?jīng)]有影響�,但由于其出現(xiàn)的頻率通常比極點(diǎn)高的多RC 低通濾波器是主要的響應(yīng)。理想的近似簡化公式為:

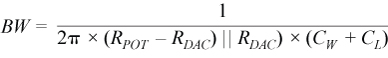

帶寬(BW)定義為:

其中CL是負(fù)載電容.

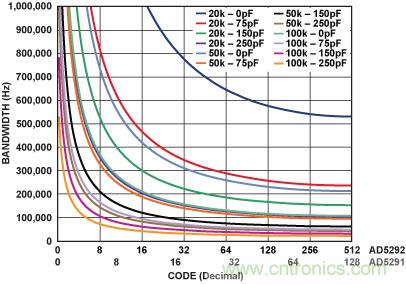

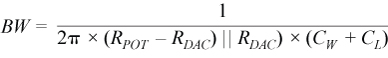

BW與代碼有關(guān)���,最差的情況是代碼在半量程時(shí)�����,AD5292的數(shù)字值為29= 512����,AD5291的數(shù)字值為27 = 128)����。圖8顯示的是低通濾波效應(yīng)����,它受代碼影響,在不同標(biāo)稱電阻與負(fù)載電容值時(shí)會發(fā)生變化.

圖8.各種電阻值的最大帶寬與負(fù)載電容

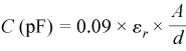

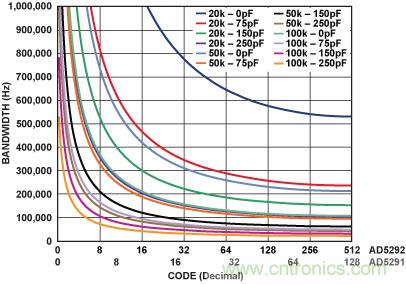

PC板的寄生走線電容也應(yīng)加以考慮����,否則最大帶寬會低于預(yù)期值,走線電容可以采用以下公式簡單計(jì)算:

其中

εR是板材的介電常數(shù)

A是走線區(qū)域(cm2)

d是層間距(cm)

如,假設(shè)FR4板材有兩個信號層和電源/接地層, εR = 4, 走線長度 = 3 cm寬度 = 1.2 mm, 層間距 = 0.3 mm; t則總走線電容約為 4 pF.

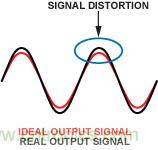

失真

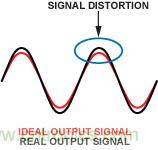

THD用于量化器件作為衰減器的非線性��。該非線性由內(nèi)部開關(guān)及其隨電壓變化的導(dǎo)通電阻 RON而產(chǎn)生����。圖9所示為放大的幅度失真示例.

圖9.失真

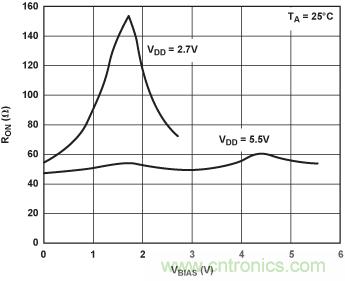

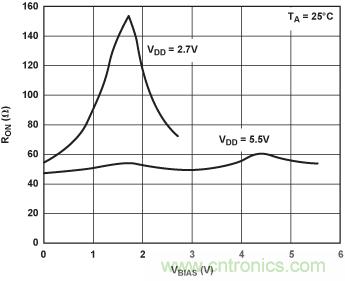

與單個內(nèi)部無源電阻相比,開關(guān)的RON很小�����,其在信號范圍內(nèi)的變化則更小�。圖10顯示的是典型的導(dǎo)通電阻特性。

圖10.CMOS電阻

電阻曲線取決于電源電壓軌�����,電源電壓最大時(shí)�,內(nèi)部開關(guān)的RON 變化最小。電源電壓降低時(shí)����,RON 變化和非線性都會隨之增加。圖11對比了低壓digiPOT在兩種供電電平下的RON

圖11.開關(guān)電阻變化與電源電壓的關(guān)系

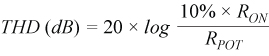

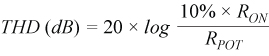

HD取決于各種因素��,因此很難量化����,若假設(shè)RON,的變化為10%���,則以下公式可用于近似計(jì)算:

一般說來,標(biāo)稱digiPOT電阻(RPOT),越大����,則分母越大,THD就越小.

權(quán)衡

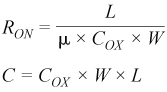

RPOT增加后��,失真和帶寬都會隨之降低�����,所以改進(jìn)一項(xiàng)指標(biāo)的同時(shí)必定會犧牲另一項(xiàng)�。因此,電路設(shè)計(jì)人員必須在兩者之間做出適當(dāng)?shù)臋?quán)衡�。這也關(guān)系到器件的設(shè)計(jì)水平,因?yàn)镮C設(shè)計(jì)人員必須平衡設(shè)計(jì)公式中的各個參數(shù):

其中

COX是氧化電容

μ是電子(NMOS)或空穴(PMOS)的遷移常數(shù)

W是寬度

L是長度

偏置

從實(shí)用的角度來看�����,我們必須充分發(fā)揮各項(xiàng)特性�。digiPOT通過容性耦合衰減交流信號時(shí)�,若信號偏置達(dá)到電源的中值����,則失真最小�����。這意味著開關(guān)工作在電阻特性線性最強(qiáng)的部分.

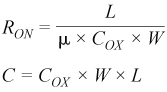

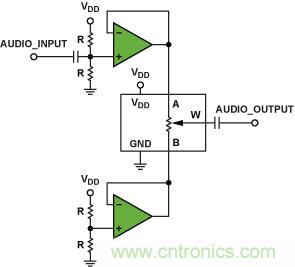

一種方法是采用雙電源供電�����,只需將電位計(jì)接地至電源共模端�,信號便會產(chǎn)生正負(fù)向擺動。如果需要單電源供電����,或者某些digiPOT不支持雙電源時(shí),可以采用另一種方法�,即添加VDD/2的失調(diào)電壓至交流信號。該失調(diào)電壓必須添加到兩個電阻端����,如圖12所示。

圖12.單電源供電交流信號調(diào)理

若需要使用信號放大器�����,雙電源供電的反相放大器優(yōu)于同相放大器(如圖13所示),原因有以下兩項(xiàng):

● THD性能更佳����,因?yàn)榉聪嘁_的虛地可將開關(guān)電阻集中在電壓范圍中間。

● 因?yàn)榉聪嘁_位于虛地�����,所以幾乎取消了游標(biāo)電容 CDLSB,令帶寬增幅較?。ū仨氉⒁怆娐贩€(wěn)定性).

圖13.采用反相放大器digiPOT可調(diào)整放大

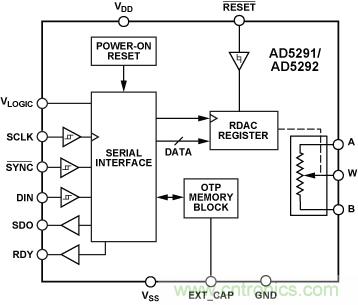

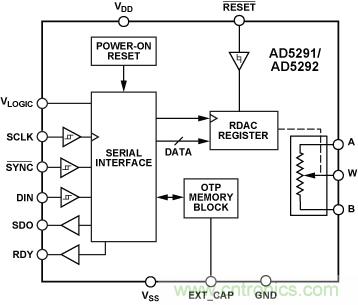

附錄——關(guān)于AD5291/AD5292

256/1024位數(shù)字電位計(jì)精度為1%,可編程20次

The AD5291/AD5292數(shù)字電位計(jì)�,如圖14所示,具有256/1024位分辨率����。端對端電阻有20 kΩ、50 kΩ和100 kΩ可供選擇���,誤差優(yōu)于1%��,溫度系數(shù)在可變電阻器模式下時(shí)為35 ppm/°C��,分壓器 模式下時(shí)為5 ppm/°C(比率)。這些器件可實(shí)現(xiàn)與機(jī)械電位計(jì)相同的電子調(diào)整功能�����,但尺寸更小且更可靠。其游標(biāo)位置可通過SPI兼容接口調(diào)整����。在熔斷熔絲,將游標(biāo)位置固定(此過程類似于將環(huán)氧樹脂涂在機(jī)械式調(diào)整器上)之前����,可進(jìn)行無限次調(diào)整。“去除環(huán)氧樹脂”過程最多可以重復(fù)20次��。AD5291/AD5292采用9 V至33 V單電源或±9 V至±16.5 V雙電源�,功耗8 μW。采用14引腳TSSOP封裝���,工作溫度范圍為–40°C至+105°C

圖14.AD5291/AD5292功能框圖

推薦閱讀: