【導讀】利用運放反饋與基準電壓生成任意大小的直流電流是一個簡單、直接的過程。但是,假設須要生成一些任意數(shù)量(以N為例)的電流沉/源(current sink/source),而每個電流沉/源的大小任意,可能須要針對不同階段的一些復雜模擬電路進行偏置。

雖然基準電壓的生成僅須一次實施即可,電流沉整個反饋部分的重復進行卻使成本與設計空間密集化。那么問題來了:是否可以使用單個反饋源來實現(xiàn)這種偏置網(wǎng)絡呢?答案是肯定的,盡管這有些復雜,也須滿足某些特定條件。該網(wǎng)絡(本文分析中僅以電流沉為例)如圖1所示。

圖1:灌電流網(wǎng)絡

最終MOSFET(金氧半場效晶體管)源電壓VS以及RSET電阻決定著各柱上的灌電流(sink current);通過去除來自外部電流沉柱的反饋(即所有N》1),已失去對VSN的直接控制。因此,RSETN必須精心選擇以生成預期的任意第N個柱的灌電流,即ISINKN。仔細觀察上面的圖1,很容易得出定義偏置網(wǎng)絡第N個柱電流與第1個柱電流的比值的等式︰

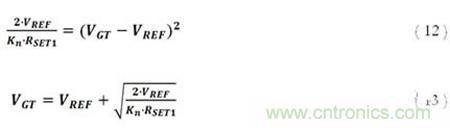

重新調(diào)整等式1,得出R1與RN電阻比MRN,等式變?yōu)椋?/div>

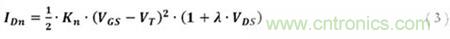

那么該偏置網(wǎng)絡第N個柱的MOSFET源電壓是什么,VSN?考慮到工作在飽和區(qū)的NMOS漏極電流等式是:

必須注意的是,這里可以很大程度上忽略通道寬度調(diào)制的影響。這是因為任何因漏極電壓上升導致的漏極電流的上升會在通過RSET電阻后下降,并導致源電壓的上升。為了使MOSFET能維持任何電流,柵極電壓必須大于源電壓與閾值電壓的和。也就是說,給定一個柵極電壓,源電壓將被限制在至少比柵極電壓小一個閾值電壓的值,且再大的漏極電壓上升也不會提升漏極電流。因此,構建相應運行條件,RSET必須足夠大,從而確保在上述限制下可允許作出以下假設:

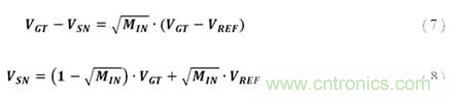

等式1中的比值可基于等式3和4改寫成:

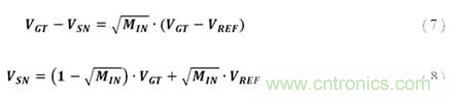

為了簡化等式5,可作出如下定義:

利用等式5進行替換與調(diào)整后,可導出VSN的等式:

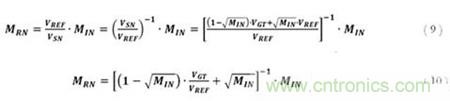

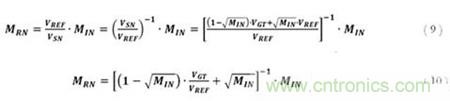

將等式8代入等式2可得出:

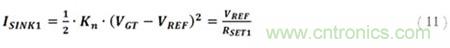

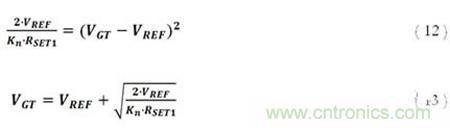

那么柵極驅(qū)動對閾值電壓的差是什么呢,VGT?這最終由偏置網(wǎng)絡第1柱的反饋決定;它本質(zhì)上是維持所需ISINK1電流需要的電壓:

重新調(diào)整等式11的項,可得出VGT的等式:

將等式13代入等式10可得出:

最后,電阻比MRN可以單純地寫成MIN的函數(shù)(加上偏置網(wǎng)絡設備的一些物理常數(shù)),如下所示:

現(xiàn)在關于RSET電阻比率的等式已導出,接下來可以探究建立任意大小的偏置電流網(wǎng)絡的含義與影響。