【導(dǎo)讀】小編又為各位新手送福利啦!本次為大家?guī)淼氖顷P(guān)于DSP入門的初級指導(dǎo),內(nèi)容大多來自于新手們在初學(xué)時期比較關(guān)心的問題和最常見的疑問,詳細(xì)到介紹初學(xué)需要看的文檔哦!涵蓋面十分之廣。如果你也對學(xué)習(xí)DSP抱有興趣,不妨來看看本篇文章來打下堅實的基礎(chǔ)吧。

開發(fā)入門需要看的文檔

講述DSP的CPU,memory、program memory addressing、data memory addressing的資料都需要看、外設(shè)資源的資料可以只看自己用到的部分。

C和匯編的編程指南需要看。

匯編指令和C語言的運行時間支持庫、DSPLIB、程序員向?qū)?、?yōu)化手冊等資料。

如何開始軟件開發(fā)

看CCS的使用指南;

明白CMD文件的編寫;

明白中斷向量表文件的編寫,并定位在正確的地方;

運行一個純simulator的程序,了解CCS的各個操作;

到TI網(wǎng)站下相關(guān)的源碼,參考源碼的結(jié)構(gòu)進行編程;

取得一塊評估板進行實際系統(tǒng)的軟件調(diào)試;

DSP的C語言同主機C語言的主要區(qū)別

DSP的C語言是標(biāo)準(zhǔn)的ANSIC,它不包括同外設(shè)聯(lián)系的擴展部分,如屏幕繪圖等。但在CCS中,為了方便調(diào)試,可以將數(shù)據(jù)通過printf命令虛擬輸出到主機的屏幕上。

DSP的C語言的編譯過程為:C編譯為ASM,再由ASM編譯為OBJ。因此C和ASM的對應(yīng)關(guān)系非常明確,非常便于人工優(yōu)化。

DSP的代碼需要絕對定位;主機的C的代碼由操作系統(tǒng)定位。

DSP的C的效率較高,非常適合于嵌入系統(tǒng)。

如何能夠相對較快地掌握DSP的硬件和軟件的設(shè)計

建議選擇合適的EVM,提供客戶完整的原理圖。

什么是DSP/BIOS

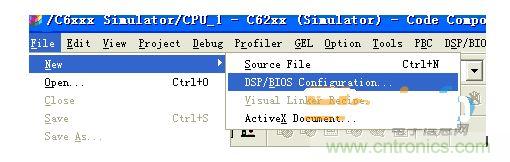

作為CCS強大開發(fā)工具的一個集成,DSP/BIOS是一個簡易的嵌入式操作系統(tǒng),它能大大方便用戶編寫多任務(wù)應(yīng)用程序同時還能增強對代碼執(zhí)行效率的監(jiān)控。DSP/BIOS工具已經(jīng)具有實時操作系統(tǒng)的很多功能,如任務(wù)調(diào)度管理、任務(wù)間的同步和通信、內(nèi)存管理、實時時鐘管理、中斷服務(wù)管理、外設(shè)驅(qū)動程序的管理等。使用DSP/BIOS開發(fā)DSP有2個重要的特點:1.所有與硬件相關(guān)的操作都必須借助DSP/BIOS本身提供的函數(shù)完成,開發(fā)者應(yīng)避免直接控制硬件。2.帶有DSP/BIOS功能的程序在運行時與傳統(tǒng)開發(fā)的程序有所不同。在傳統(tǒng)開發(fā)中程序是順序執(zhí)行,基于DSP/BIOS開發(fā)的程序由BIOS來調(diào)度,不再按照編寫的順序來執(zhí)行。File-NEW-DSP/BIOSConfiguration。

圖1

建立新的配置文件,根據(jù)開發(fā)的DSP不同芯片,對BIOS進行配置,如圖1所示。

[page]

PCI同ISA的區(qū)別?

PCI是同步總線;ISA是異步總線。PCI的傳輸率較高。PCI可以即插即用。PCI的成本較高。

何為USB?

USB是通用串行總線的簡稱。它具有以下特點:傳輸速度快;連接方便;成本低。接口簡單;兼容性好;可以適應(yīng)于不同的計算機平臺;開發(fā)容易;

CPLD同F(xiàn)PGA的區(qū)別?

CPLD的邏輯單元較大。

CPLD的容量較小。

CPLD的時序確定,延時可預(yù)測。

CPLD適合于組合邏輯和計算器設(shè)計。

USB的有哪些種類?

按種類分有:接口型:只提供接口。較便宜;使用復(fù)雜。芯片型:本身是一個單片機。使用簡單。

按用途分有:Hub型:為了構(gòu)成USBHub。設(shè)備型:設(shè)備端接口。主機型:主機端接口。

按速度分有:低速型:1.5M。用于鼠標(biāo)、鍵盤等慢速計算機外設(shè)。全速型:12M。用于數(shù)據(jù)傳輸。高速型:480M。

5V/3.3V如何混接?

TIDSP的發(fā)展同集成電路的發(fā)展一樣,新的DSP都是3.3V的,但目前還有許多外圍電路是5V的,因此在DSP系統(tǒng)中,經(jīng)常有5V和3.3V的DSP混接問題。在這些系統(tǒng)中,應(yīng)注意:

DSP輸出給5V的電路(如D/A),無需加任何緩沖電路,可以直接連接。DSP輸入5V的信號(如A/D),由于輸入信號的電壓>4V,超過了DSP的電源電壓,DSP的外部信號沒有保護電路,需要加緩沖,如74LVC245等,將5V信號變換成3.3V的信號。

仿真器的JTAG口的信號也必須為3.3V,否則有可能損壞DSP。

為什么要片內(nèi)RAM大的DSP效率高?

目前DSP發(fā)展的片內(nèi)存儲器RAM越來越大,要設(shè)計高效的DSP系統(tǒng),就應(yīng)該選擇片內(nèi)RAM較大的DSP。片內(nèi)RAM同片外存儲器相比,有以下優(yōu)點:

片內(nèi)RAM的速度較快,可以保證DSP無等待運行。

對于C2000/C3x/C5000系列,部分片內(nèi)存儲器可以在一個指令周期內(nèi)訪問兩次,使得指令可以更加高效。

片內(nèi)RAM運行穩(wěn)定,不受外部的干擾影響,也不會干擾外部。

DSP片內(nèi)多總線,在訪問片內(nèi)RAM時,不會影響其它總線的訪問,效率較高。

[page]

為什么DSP從5V發(fā)展成3.3V?

超大規(guī)模集成電路的發(fā)展從1um,發(fā)展到目前的0.1um,芯片的電源電壓也隨之降低,功耗也隨之降低。DSP也同樣從5V發(fā)展到目前的3.3V,核心電壓發(fā)展到1V。目前主流的DSP的外圍均已發(fā)展為3.3V,5V的DSP的價格和功耗都價格,以逐漸被3.3V的DSP取代。

如何選擇DSP的電源芯片?

TMS320LF24xx:TPS7333QD,5V變3.3V,最大500mA。TMS320VC33:TPS73HD318PWP,5V變3.3V和1.8V,最大750mA。TMS320VC54xx:TPS73HD318PWP,5V變3.3V和1.8V,最大750mA;TPS73HD301PWP,5V變3.3V和可調(diào),最大750mA。TMS320VC55xx:TPS73HD301PWP,5V變3.3V和可調(diào),最大750mA。TMS320C6000:PT6405B,PT6407E,最大3A。

如何選擇外部時鐘?

DSP的內(nèi)部指令周期較高,外部晶振的主頻不夠,因此DSP大多數(shù)片內(nèi)均有PLL。但每個系列不盡相同。

TMS320C2000系列:TMS320C20x:PLL可以÷2,×1,×2和×4,因此外部時鐘可以為5MHz-40MHz。TMS320F240:PLL可以÷2,×1,×1.5,×2,×2.5,×3,×4,×4.5,×5和×9,因此外部時鐘可以為2.22MHz-40MHz。TMS320F241/C242/F243:PLL可以×4,因此外部時鐘為5MHz。TMS320LF24xx:PLL可以由RC調(diào)節(jié),因此外部時鐘為4MHz-20MHz。TMS320LF24xxA:PLL可以由RC調(diào)節(jié),因此外部時鐘為4MHz-20MHz。

TMS320C3x系列:TMS320C3x:沒有PLL,因此外部主頻為工作頻率的2倍。TMS320VC33:PLL可以÷2,×1,×5,因此外部主頻可以為12MHz-100MHz。

TMS320C5000系列:TMS320C54x:PLL可以÷2,×1-32,因此外部主頻可以為0.25MHz-200MHz。TMS320VC54xx:PLL可以÷4,÷2,×1-32,因此外部主頻可以為0.625MHz-50MHz。TMS320VC55xx:PLL可以÷4,÷2,×1-32,因此外部主頻可以為6.25MHz-200MHz。

TMS320C6000系列:TMS320C62xx:PLL可以×1,×4,×6,×7,×8,×9,×10和×11,因此外部主頻可以為11.8MHz-75MHz。TMS320C67xx:PLL可以×1和×4,因此外部主頻可以為12.5MHz-41.7MHz。TMS320C64xx:PLL可以×1,×6和×12,因此外部主頻可以為30MHz-75MHz。

如何選擇DSP的外部存儲器?

DSP的速度較快,為了保證DSP的運行速度,外部存儲器需要具有一定的速度,否則DSP訪問外部存儲器時需要加入等待周期。

對于C2000系列:C2000系列只能同異步的存儲器直接相接。C2000系列的DSP目前的最高速度為30MHz,為保證DSP無等待運行,需要外部存儲器的速度<30ns。建議可以用的存儲器有:CY7C199-15:32K×8,15ns,5V;CY7C1021-15:64K×16,15ns,5V;CY7C1021V33-15:64K×16,15ns,3.3V。

對于C3x系列:C3x系列只能同異步的存儲器直接相接。C3x系列的DSP的最高速度,5V的為40MHz,3.3V的為75MHz,為保證DSP無等待運行,分別需要外部存儲器的速度<25ns和<12ns。

建議可以用的存儲器有:ROM:AM29F400-70:256K×16,70ns,5V,加入一個等待;AM29LV400-55:256K×16,55ns,3.3V,加入兩個等待(目前沒有更快的Flash)。SRAM:CY7C199-15:32K×8,15ns,5V;CY7C1021-15:64K×16,15ns,5V;CY7C1009-15:128K×8,15ns,5V;CY7C1049-15:512K×8,15ns,5V;CY7C1021V33-15:64K×16,15ns,3.3V;CY7C1009V33-15:128K×8,15ns,3.3V。

對于C54x系列:C54x系列只能同異步的存儲器直接相接。C54x系列的DSP的速度為100MHz或160MHz,為保證DSP無等待運行,需要外部存儲器的速度<10ns或<6ns。

建議可以用的存儲器有:ROM:AM29LV400-55:256K×16,55ns,3.3V,加入5或9個等待(目前沒有更快的Flash)。SRAM:CY7C1021V33-12:64K×16,12ns,3.3V,加入一個等待;CY7C1009V33-12:128K×8,12ns,3.3V,加入一個等待。

對于C55x和C6000系列:TI的DSP中只有C55x和C6000可以同同步的存儲器相連,同步存儲器可以保證系統(tǒng)的數(shù)據(jù)交換效率更高。ROM:AM29LV400-55:256K×16,55ns,3.3V。SDRAM:HY57V651620BTC-10S:64M,10ns。SBSRAM:CY7C1329-133AC,64k×32;CY7C1339-133AC,128k×32。FIFO:CY7C42x5V-10ASC,32k/64k×18。

在看過本篇文章之后,各位是不是更堅定了自己學(xué)習(xí)DSP的信心呢?小編將繼續(xù)收集整理關(guān)于DSP初學(xué)階段的一些疑問,幫助大家加快學(xué)習(xí)的步伐,并且走更少的彎路。