【導讀】PFC比值的大小能夠直接反映電力的有效利用程度。很多電源類產(chǎn)品在生產(chǎn)時,都會對PFC有所要求。本篇文章主要介紹PFC段的設計中經(jīng)常會遇到的兩個問題。以及針對這兩個PFC段設計中常見的問題給出的解決方案。

功率因數(shù)校正的縮寫是PFC,PFC其實是一種數(shù)值關系,是有效的功率和總耗電量之比。PFC比值的大小能夠直接反映電力的有效利用程度?,F(xiàn)代人的生活節(jié)奏越來越快,對科技產(chǎn)品的要求也越來越高。很多電源類產(chǎn)品在生產(chǎn)時,都會對PFC有所要求。

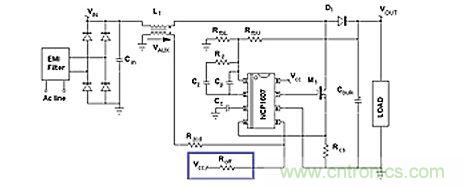

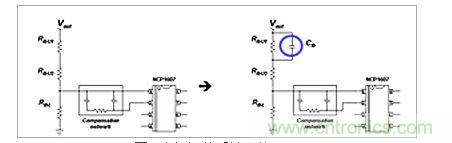

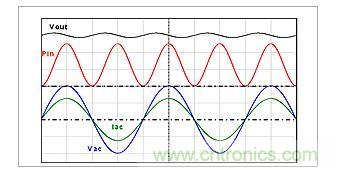

圖1 ZCD引腳上的調(diào)整

提高PFC的方法多種多樣,本篇文章當中將為大家介紹一種能夠對PFC段性能進行提高的方法,這種方法通過改善線路的工作狀態(tài)來進行調(diào)整,如圖1所示,在VCC與引腳5(ZCD引腳)之間布設一顆電阻,能夠減輕或抑制這個現(xiàn)象。這樣一來,ZCD引腳上就產(chǎn)生了偏置。

在測試的應用中,VCC為15V,且Rzcd=68kΩ。在VCC與引腳5之間增加一顆電阻Roff=680kΩ,就改變了施加在引腳5(ZCD引腳)上的電壓。退磁相位期間ZCD引腳上施加的實際VAUX電壓就變?yōu)椋?/div>

然后,施加在引腳5上的電壓就為偏置。事實上,這就像是VAUX電壓與減小了1.36V的ZCD閾值比較。這樣一來,新的實際ZCD閾值就是:

Vpin5上升:最低值為0.74V,典型值為0.94V,最大值為1.14V。

Vpin5下降:最低值為0.14V,典型值為0.24V,最大值為0.44V。

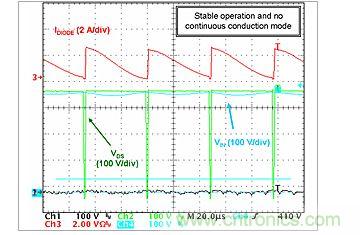

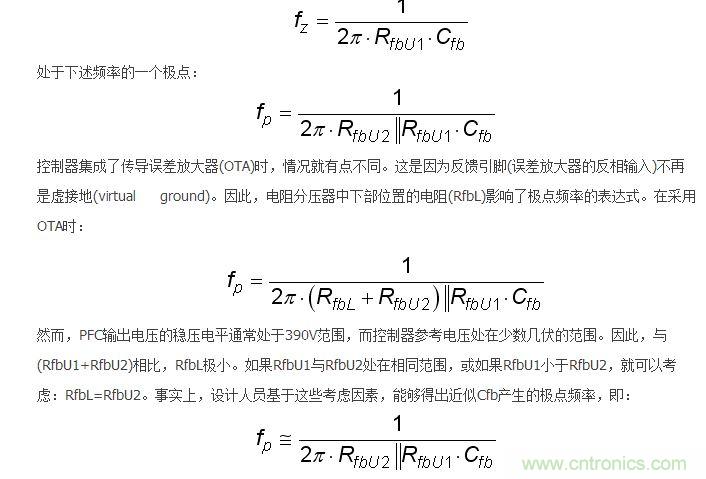

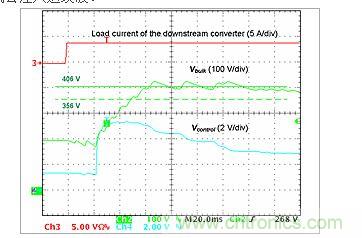

圖2 調(diào)整改善器件工作

ZCD閾值的下降起到了增加ZCD精度的作用,與此同時,能夠很有效的抑制CCM的工作。在相同條件下獲得的波特圖(見圖2)就證實了這一點。

在這里需要注意的是,Vpin5下降(案例中是1.5V)時,偏置必須保持在低于ZCD最低閾值。這是為了確保新的實際ZCD閾值(Vpin5下降時) 保持高于0V。否則,系統(tǒng)可能難于檢測磁芯復位并因此啟動新的開關序列。出于這個目的,應當考慮到VCC的變化。

[page]

啟動時的大過沖

正弦電流能夠為負載提供相應的平均需求方波正弦功率,PFC段也從輸入線路正弦波電壓裕安來吸收它們。輸出電容(大電容)“吸收”實際提供的功率與負載消耗的功率之差值。

饋送給負載的功率低于需求時,輸出電容放電,補償功率差額。提供的功率超過負載功耗時,輸出電容充電,存儲多余的能量。

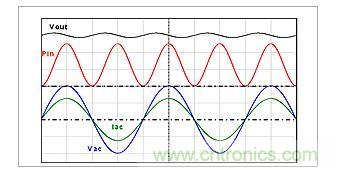

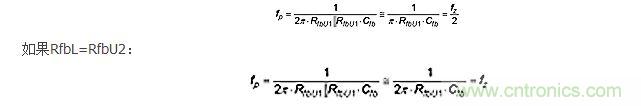

圖3輸出電壓紋波

所以,輸出電壓呈現(xiàn)出輸入線路頻率2倍的低頻交流含量。不利的是,PFC電流整形(current-shaping)方法均基于控制信號無紋波的假設。否則,就不能夠優(yōu)化功率因數(shù),因為輸入線路電流重新復制了控制信號失真。這就是眾所周知的PFC電路動態(tài)性能差的原因。它們的穩(wěn)壓環(huán)路帶寬設得極低,從而抑制100Hz或120Hz紋波,否則輸出電壓就會注入這紋波。

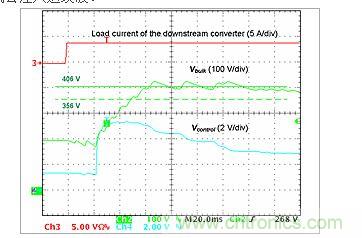

圖4 啟動相位期間的過沖

由于系統(tǒng)極慢,PFC段遭受陡峭的負載或輸入電壓變化時,會在大電容上呈現(xiàn)出大的過沖(over-shoot)或欠沖(under-shoot)。啟動序列就是這些瞬態(tài)中的一種,能夠產(chǎn)生大的電壓過應力(over-stress)。

圖4展示能在啟動相位期間觀察到的那類過沖。這波特圖是使用由NCP1607驅動,負載是下行轉換器的PFC段獲得的。

承受啟動過沖

大部分人認為,應用軟啟動是在控制器的選擇當中最需要存在的一個功能,但是實際上,它并非必須存在的功能特性。此外,從定義來看,這種功能減緩了啟動速度,而這并非總是可以接受。

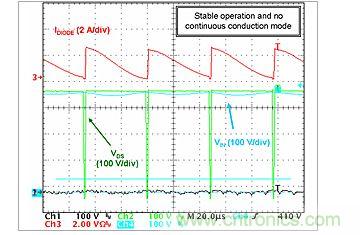

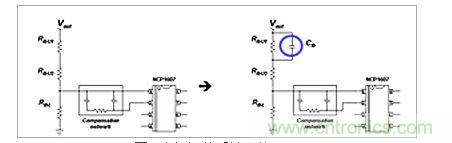

圖5 小幅調(diào)整反饋網(wǎng)絡

[page]

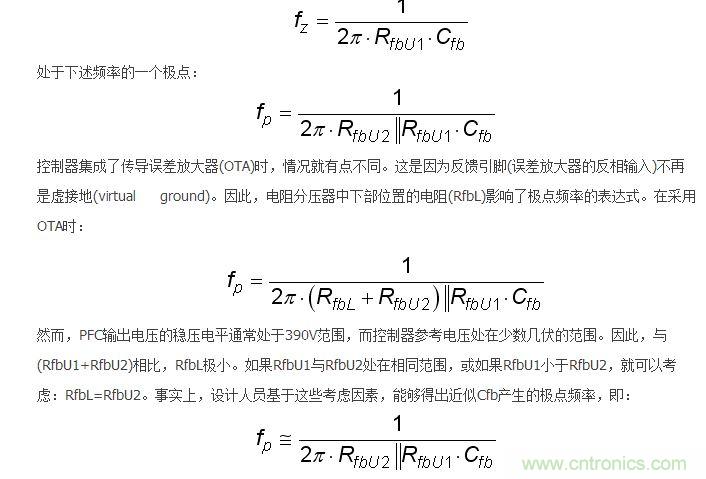

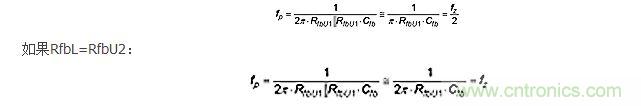

另一個需要面對的選擇是,是否需要在反饋感測電阻分壓器處增加一個電容。如圖5所示。在這個圖中,我們假定感測網(wǎng)絡中上部的電阻分割為兩個電阻,而電容Cfb并聯(lián)連接在其中一個電阻的兩端。如果控制電路中嵌入了傳統(tǒng)的誤差放大器,然后分析此時電容Cfb的影響。在穩(wěn)態(tài),Cfb改變了傳遞函數(shù)。通過檢測,我們立即注意到它增加了:

處于下述頻率的一個零點:

最后,兩種配置中都獲得相同的極點。這些條件(RfbU1≈RfbU2)或(RfbU1≤RfbU2)并非限制性條件。相反,滿足這些條件是明智之舉,因為RfbU1兩端的電壓及相應的Cfb兩端的電壓取決于RfbU1值與(RfbU1+RfbU2+RfbL)總電阻值的相對比較關系。這就是為什么它們是現(xiàn)實可行的原因。

如果RfbU1與RfbU2這兩個電阻擁有類似阻值:

如果RfbU1與RfbU2處在相同范圍,低頻增益就略微增加,交越頻率就跟隨fp與fz的相同比率增加。如果與RfbU2相比RfbU1極小,我們就獲得在控制至輸出傳遞函數(shù)中抵消(cancel)的極點和零點。這樣,增加Cfb就對環(huán)路和交越頻率沒有影響。事實上,特別是在RfbL=RfbU2時,這個增加的電容并不會大幅改變PFC段的動態(tài)性能。

但是,這個新增加的電容并非是多余的,它有著比較重要的作用,當啟動相位時,這個電容才能真正的發(fā)揮作用。當輸出電壓上升時,Cfb電容也充電。Cfb充電電流增加到反饋電流中,所以穩(wěn)壓電平臨時降低。這增加的電流與Cfb電容值成正比,并取決于輸出電壓的陡峭度,因此,在輸出電壓快速充電時,這個影響更引人注目。

本篇文章主要介紹了PFC段的設計中經(jīng)常會遇到的兩個問題。當功率因數(shù)退化或著產(chǎn)生明顯的噪音時,可在電路當中增加一個電阻來解決這個問題。此外,在啟動序列期間,PFC段也有可能產(chǎn)生比較大的過沖,此時就需要在電路當中添加電容來達到抑制的目的。之所以對這兩種方法進行介紹,是因為即便是已經(jīng)到了設計的后半段時期,這兩種調(diào)整方法還是非常容易在電路中得以實現(xiàn)的。