【導(dǎo)讀】本文為大家講解的是一款可控制吸收電容充放電的電路圖設(shè)計,該電路設(shè)計具體情況大家可見下文。電路中,VF1是一次側(cè)主MOSFET,來自PWM集成控制器的脈沖使其通/斷工作。為使VF2的通/斷時間與VF1相反...

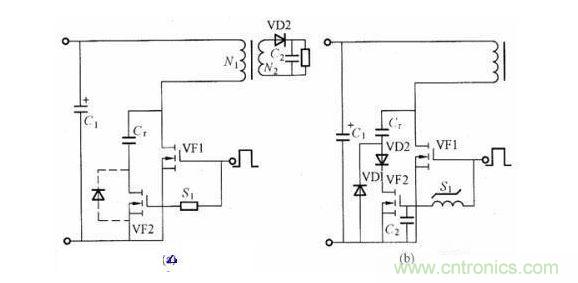

圖(a)所示電路中,VF1是一次側(cè)主MOSFET,來自PWM集成控制器的脈沖使其通/斷工作。為使VF2的通/斷時間與VF1相反,增設(shè)雙向延時電路S1。現(xiàn)假設(shè)VF1為截止?fàn)顟B(tài),VF2為導(dǎo)通狀態(tài),吸收電容Cr充電到VF1的漏極-源極間電壓,由此,也吸收加在VF1上的浪涌電壓。在由延時電路確定的延時時間后VF2截止,但這時,Cr兩端電壓等于加在VF1上的電壓,因此,為零電壓和零電流開關(guān)器件斷開方式。

VF1截止后,二次側(cè)二極管VD2的電流降為零,變壓器無勵磁能量。此時一次主繞組N1感應(yīng)的回掃電壓變?yōu)榱悖愿哂贑1上電壓進(jìn)行充電的吸收電容 C1對一次主繞組N1反向放電,這樣,放電電流經(jīng)VF2的寄生二極管(虛線所示)流通。Cr放電開始時,VF2必須截止。由于Cr放電,電容Cr與一次主繞組的電感Lp產(chǎn)生諧振。

(a)原理電路;(b)實用電路

圖 控制吸收電容充放電的電路圖

若VF2為導(dǎo)通狀態(tài),諧振繼續(xù)衰減振蕩,但VF2截止?fàn)顟B(tài)時,電容Cr兩端電壓為零時振蕩停止。若Cr停止諧振,則以VF1和VF2的輸入較小容量電容繼續(xù)產(chǎn)生較短周期的諧振。VF1再度導(dǎo)通時,軔小電容放電電流流經(jīng)VF1本身而消耗掉。VF1導(dǎo)通時,其小容量電容充電的電壓隨導(dǎo)通時間而改變,但 Cr兩端電壓降到最低電壓,因此,可以減小Cr產(chǎn)生的損耗。也就是說,即使采用較大容量的電容Cr損耗也不會增大。

圖(a)所示為采用VF2寄生二極管使Cr放電形式的電路。一般的M0S-FET寄生二極管恢復(fù)特性不適宜高頻,因此,增設(shè)低耗二極管作為電容放電二極管,即圖(b)中的二極管VD1。為使放電電流全部流經(jīng)二極管VD1,在VF2回路中增加了逆阻斷二極管VD2.逆阻斷二極管VD2的耐壓大于VD1 的正向壓降即可,因此,選用肖特基二極管(SBD)。另外,雙向延時元件宜采用可飽和電抗器,延時元件和YF2的輸入電容共同決定延時時間,需要較長延時時間時,可在柵極增接電容。輸出電流一減小,VF1的導(dǎo)通時間就變短。這導(dǎo)通時間若短于延時時間,則VF1截止后,VF2導(dǎo)通,因此,VF1漏極-源極間電壓UDS的波形偏離正常波形,功耗也稍增大。為降低最小輸出電流,延時時間要非常短,這樣,就不能充分有效利用電容Cr。這里,作為大致目標(biāo),最小輸出電流設(shè)定為最大輸出電流的2%~3%。