【導(dǎo)讀】隨著電子技術(shù)的飛速發(fā)展�����,存儲(chǔ)器的種類日益繁多,每一種存儲(chǔ)器都有其獨(dú)有的操作時(shí)序�����,為了提高存儲(chǔ)器芯片的測(cè)試效率,一種多功能存儲(chǔ)器芯片的測(cè)試系統(tǒng)應(yīng)運(yùn)而生��。

本文提出了一種多功能存儲(chǔ)器芯片的測(cè)試系統(tǒng)硬件設(shè)計(jì)與實(shí)現(xiàn)����,對(duì)各種數(shù)據(jù)位寬的多種存儲(chǔ)器芯片(SRAM、MRAM�����、NOR FALSH����、NAND FLASH、EEPROM等)進(jìn)行了詳細(xì)的結(jié)口電路設(shè)計(jì)(如何掛載到NIOSII的總線上)�,最終解決了不同數(shù)據(jù)位寬的多種存儲(chǔ)器的同平臺(tái)測(cè)試解決方案,并詳細(xì)地設(shè)計(jì)了各結(jié)口的硬件實(shí)現(xiàn)方法���。

引言

隨著電子技術(shù)的飛速發(fā)展���,存儲(chǔ)器類芯片的品種越來(lái)越多,其操作方式完全不一樣���,因此要測(cè)試其中一類存儲(chǔ)器類芯片就會(huì)有一種專用的存儲(chǔ)器芯片測(cè)試儀�����。本文設(shè)計(jì)的多種存儲(chǔ)器芯片測(cè)試系統(tǒng)是能夠?qū)RAM�����、Nand FLASH�、Nor FLASH、MRAM��、EEPROM等多種存儲(chǔ)器芯片進(jìn)行功能測(cè)試�,而且每一類又可兼容8位、16位��、32位�、40位等不同寬度的數(shù)據(jù)總線,如果針對(duì)每一種產(chǎn)品都單獨(dú)設(shè)計(jì)一個(gè)測(cè)試平臺(tái)���,其測(cè)試操作的復(fù)雜程度是可想而知的。為達(dá)到簡(jiǎn)化測(cè)試步驟�、減小測(cè)試的復(fù)雜度、提高測(cè)試效率���、降低測(cè)試成本���,特設(shè)計(jì)一種多功能的存儲(chǔ)器類芯片測(cè)試系統(tǒng)����,實(shí)現(xiàn)在同一平臺(tái)下完成所有上述存儲(chǔ)器芯片的方便快捷地測(cè)試�。

設(shè)計(jì)原理

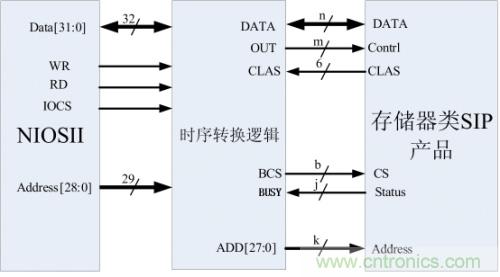

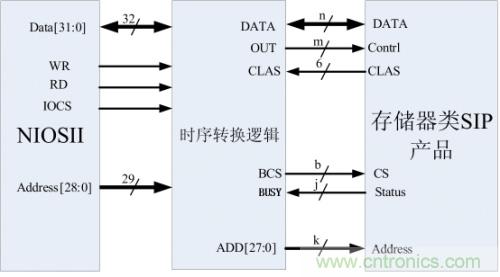

此設(shè)計(jì)方案根據(jù)上述各種存儲(chǔ)器獨(dú)自的讀寫(xiě)時(shí)序訪問(wèn)特性,通過(guò)FPGA的靈活編程特性�����,適當(dāng)?shù)卣{(diào)整NIOSII的外部總線時(shí)序��,最終實(shí)現(xiàn)基于NIOSII的外部總線訪問(wèn)各種存儲(chǔ)器讀寫(xiě)時(shí)序的精確操作���。如圖2-1����。通過(guò)FPGA自定義一個(gè)可以掛載所有存儲(chǔ)器芯片的總線接口-ABUS����,如表1。而且在同一個(gè)接口上能夠自動(dòng)識(shí)別各種接入的被測(cè)試存儲(chǔ)器芯片���,它們通過(guò)類別輸入信號(hào)(CLAS)來(lái)區(qū)分,每一種存儲(chǔ)器芯片對(duì)應(yīng)一種獨(dú)特的操作時(shí)序�。下面是幾種存儲(chǔ)器芯片的接口連接方式及信號(hào)描述。其它的存儲(chǔ)器芯片都可以用類似的接法掛載到ABUS總線上�,最終完成測(cè)試。

圖 2?1 NIOSII的總線掛載各類存儲(chǔ)器芯片連接示意圖

表1:ABUS接口信號(hào)說(shuō)明表

40位NAND FLASH連接設(shè)計(jì)

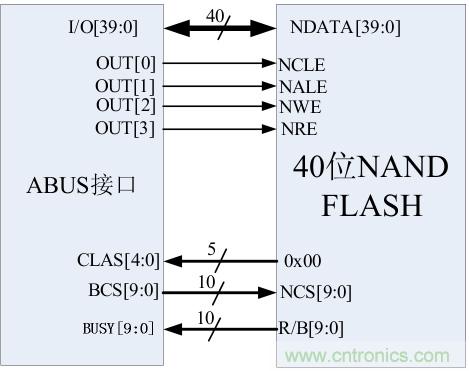

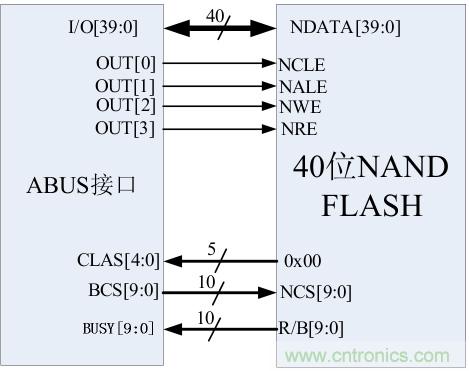

如圖2-2所示�����,40位NAND FLASH與NIOSII 通過(guò)ABUS(FPGA)橋接,把外部總線的時(shí)序完全轉(zhuǎn)換成NAND FLASH的操作時(shí)序�����。40位NAND FLASH芯片品由五個(gè)獨(dú)立的8位NAND FLASH芯片拼接構(gòu)成�����。5個(gè)8位器件的外部IO口拼接成40位的外部IO口�,而各自的控制線(NCLE,NALE�����,NRE�,NWE)連接在一起構(gòu)成一組控制線(NCLE���,NALE���,NRE��,NWE)���,片選相互獨(dú)立引出成NCS0-NCS9,忙信號(hào)獨(dú)立引出為R/B0-R/B9。

如表2��,詳述了40位NAND FLASH與ABUS的連接關(guān)系���。

圖 2?2 ABUS與40位NAND FLASH接口圖

表2��,40位NAND FLASH接口連接表

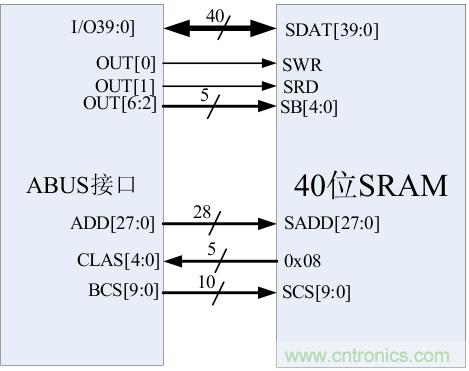

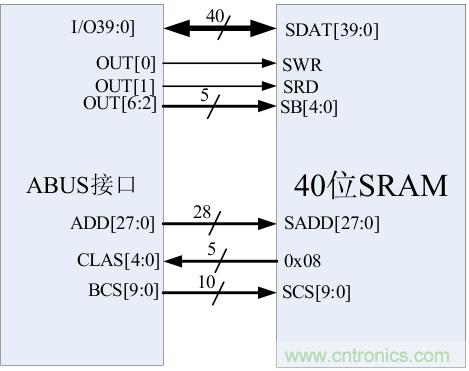

40位SRAM與NIOSII連接

40位SRM模塊與NIOSII通過(guò)ABUS連接���,實(shí)現(xiàn)正確的時(shí)序讀寫(xiě)操作。測(cè)試時(shí)�����,一次只測(cè)試8位���,分5次完成所有空間的測(cè)試���。如圖2-4���。表4是詳細(xì)的信號(hào)連接說(shuō)明。

圖 2?4 ABUS與40位SRAM連接

表4�,40位SRAM接口連接表

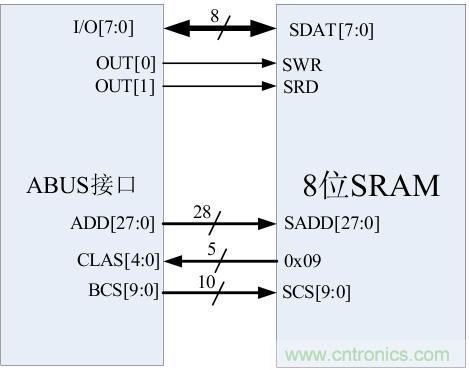

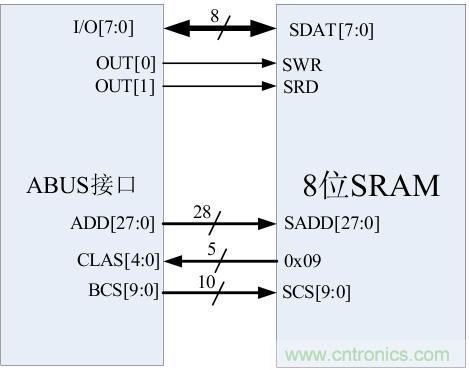

8位SRAM與NIOSII連接

8位SRM模塊與NIOSII通過(guò)ABUS(FPGA)連接,實(shí)現(xiàn)正確的時(shí)序讀寫(xiě)操作�。如圖2-5。表5是信號(hào)連接說(shuō)明�。

圖 2?5 ABUS與8位SRAM連接

8位SRAM與NIOSII連接

8位SRM模塊與NIOSII通過(guò)ABUS(FPGA)連接,實(shí)現(xiàn)正確的時(shí)序讀寫(xiě)操作���。如圖2-5���。表5是信號(hào)連接說(shuō)明。

圖 2?5 ABUS與8位SRAM連接

表5�,8位SRAM接口連接表

硬件電路設(shè)計(jì)

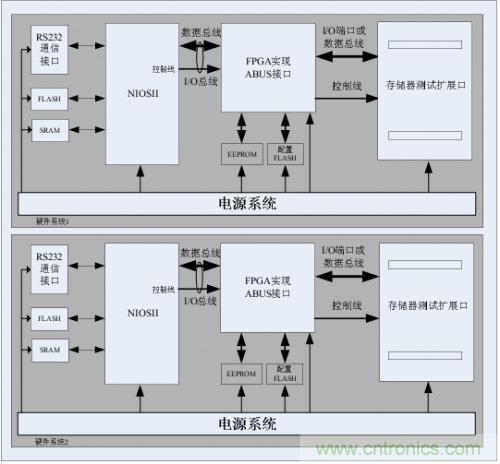

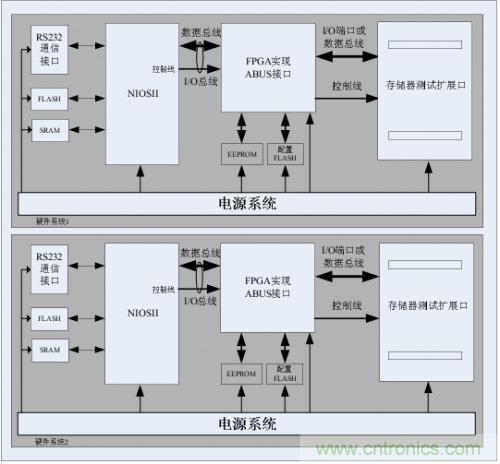

在測(cè)試NAND FLASH時(shí),測(cè)試時(shí)間長(zhǎng)達(dá)十個(gè)小時(shí)不等����。在此為提高測(cè)試效率,增加測(cè)試速度�����,本設(shè)計(jì)采用兩套完全一樣且獨(dú)立的硬件系統(tǒng)構(gòu)成��?��?赏瑫r(shí)最多測(cè)試2片NAND FLASH器件�。每一個(gè)硬件系統(tǒng)由一個(gè)微處理器(NIOSII)加一個(gè)大容量FPGA及一個(gè)存儲(chǔ)器測(cè)試擴(kuò)展接口(即ABUS接口)三大模塊構(gòu)成����。如圖3-1。RS232通信接口實(shí)現(xiàn)測(cè)試系統(tǒng)與上位機(jī)的數(shù)據(jù)交換���,完成人機(jī)交互操作���。電源系統(tǒng)產(chǎn)生各種合適的電壓,滿足各芯片的電源供給���。

圖 3?1 硬件方塊圖

處理器模塊電路

處理器模塊電路由FPGA內(nèi)嵌的NIOSII軟核(CPU)��、兩路RS232通信��、一個(gè)FLASH芯和一個(gè)SRAM芯片組成���。CPU是整個(gè)系統(tǒng)的核心管理者���,向下負(fù)責(zé)各種存儲(chǔ)器芯片的讀寫(xiě)測(cè)試,向上負(fù)責(zé)與上位機(jī)通信��,實(shí)現(xiàn)人機(jī)交互���。通信由其中一個(gè)RS232電路完成�����,另一個(gè)RS232電路用來(lái)實(shí)現(xiàn)系統(tǒng)調(diào)試和軟件固化�。FLASH芯片用來(lái)存儲(chǔ)程序代碼及重要的數(shù)據(jù)����。而SRAM芯片在CPU上電工作以后,通過(guò)CPU加載FLASH的程序���,最終給CPU的程序代碼提供快速的運(yùn)行環(huán)境����。

基于FPGA的ABUS接口模塊

ABUS接口模塊由FPGA芯片�����、配置FLASH及數(shù)據(jù)存儲(chǔ)EEPROM芯片構(gòu)成。ABUS要實(shí)現(xiàn)NIOSII的外部總線與多種存儲(chǔ)器模塊的接口對(duì)接��,每一種特定的存儲(chǔ)器有一個(gè)特定的時(shí)序邏輯��,而每一種時(shí)序邏輯可以通過(guò)FPGA的硬件代碼(IP核)來(lái)實(shí)現(xiàn)�,具體的每一個(gè)存儲(chǔ)器模塊在測(cè)試時(shí)會(huì)給ABUS接口一個(gè)固定的類別信號(hào)CLAS�,ABUS接口根據(jù)這個(gè)類別信號(hào)識(shí)別出各種SIP存儲(chǔ)器模塊,最終切換出正確的對(duì)應(yīng)特定產(chǎn)品的時(shí)序邏輯����,來(lái)完成NIOSII通過(guò)外部總線來(lái)對(duì)存儲(chǔ)器芯片的讀寫(xiě)測(cè)試。而配置FLASH實(shí)現(xiàn)FPGA在上電時(shí)硬件程序的加載工作及掉電數(shù)據(jù)保護(hù)�。EEPROM用來(lái)存儲(chǔ)一些重要的系統(tǒng)參數(shù)。

SIP存儲(chǔ)器測(cè)試擴(kuò)展接口

存儲(chǔ)器測(cè)試擴(kuò)展接口在硬件上由兩排雙排座構(gòu)成����。一共是120個(gè)管腳。ABUS接口與測(cè)試擴(kuò)展接口相連接:40個(gè)管腳與雙向的數(shù)據(jù)或I/O線相連���、8個(gè)管腳與8根信號(hào)輸入控制線相連�、16個(gè)管腳與16根片選信號(hào)輸出線相連�����、5個(gè)管腳與5根類別輸入信號(hào)相連、16個(gè)管腳與16根狀態(tài)輸入信號(hào)線相連����、27個(gè)管腳與27根地址線相連。其它的管腳可分配成電源和地線����,以及信號(hào)指示等。

ABUS接口IP核的設(shè)計(jì)

每一種SIP存儲(chǔ)器對(duì)應(yīng)于一個(gè)特定的ABUS接口IP核�����,以實(shí)現(xiàn)正確的時(shí)序讀寫(xiě)操作�。這個(gè)IP核有一個(gè)統(tǒng)一的接口約定,都是由兩個(gè)固定的接口構(gòu)成��,其中與NIOSII連接的是外部總線接口���,其操作按照NIOSII的外部總線時(shí)序規(guī)范來(lái)實(shí)現(xiàn)�����,另一個(gè)接口就是上文提及的ABUS接口���,在相應(yīng)的CLAS信號(hào)有效的情況下��,它負(fù)責(zé)把NIOSII的外部總線讀寫(xiě)時(shí)序轉(zhuǎn)換成對(duì)應(yīng)存儲(chǔ)器芯片的時(shí)序����。IP核的工作就是完成這些讀寫(xiě)操作的轉(zhuǎn)換���。表5是各種SIP存儲(chǔ)器對(duì)應(yīng)的類別信(CLAS)號(hào)輸入值�,在設(shè)計(jì)接口轉(zhuǎn)接板時(shí)要按這個(gè)值設(shè)定�����,ABUS才會(huì)切換出正確的讀寫(xiě)時(shí)序��。

七位類別示別信號(hào)含義:T_XX_WW_CC,T為1表示高低測(cè)試測(cè)試�,為0表示常溫下的功能測(cè)試����。XX表示存儲(chǔ)器種類,WW表示總線寬度�����,CC表示容量種類���。

表5 各種SIP存儲(chǔ)器對(duì)應(yīng)的CLAS信號(hào)值

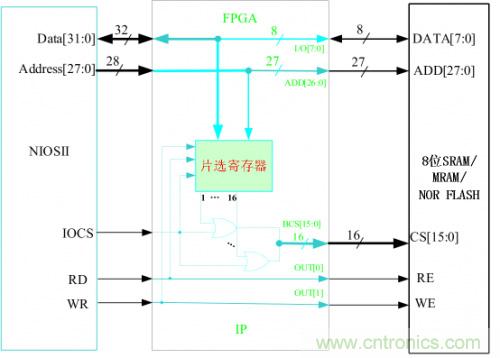

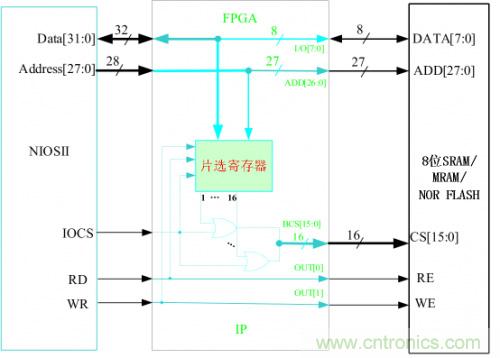

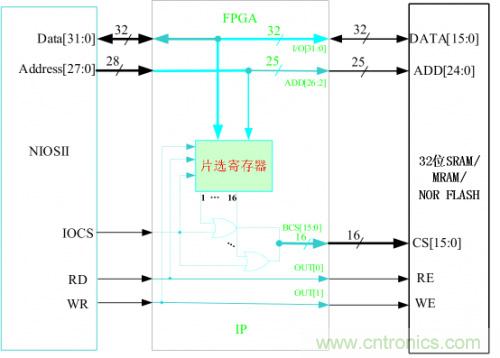

8位SRAM/MRAM/NOR FLASH接口IP核設(shè)計(jì)

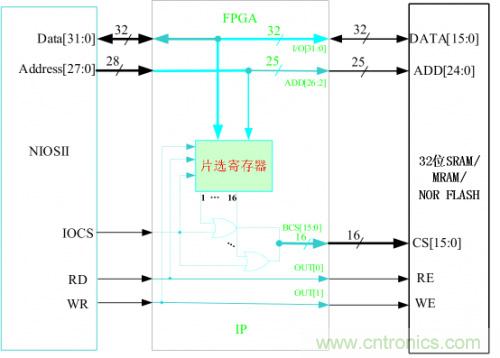

如圖4-1�,SRAM、MRAM和NOR FLASH的接口操作基本一致����,NIOSII的總線時(shí)序完全滿足。故在FPGA內(nèi)部只要簡(jiǎn)單地把相應(yīng)的控制線和數(shù)據(jù)線相連就可以了����,唯獨(dú)只要設(shè)計(jì)一個(gè)片選寄存器,用來(lái)區(qū)分存儲(chǔ)器芯片的16個(gè)片選���。每一個(gè)片選可以訪問(wèn)的空間為128MByte����。片選寄存器的地址為(基址+0x0FFFFFFC),基地址設(shè)在NIOSII外部總線的最高地址位����。

圖 4?1 8位SRAM/MRAM/NOR FLASH接口IP

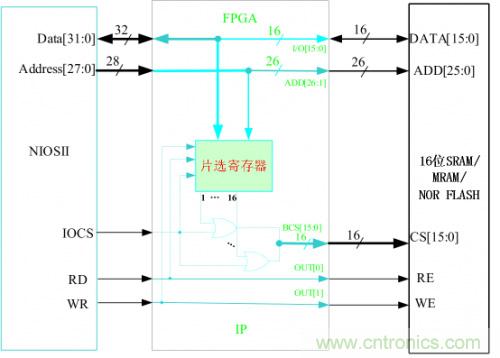

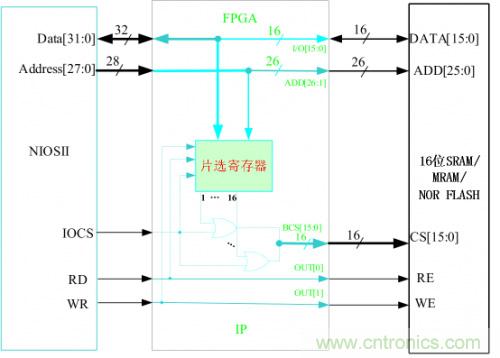

16位SRAM/MRAM/NOR FLASH接口IP核設(shè)計(jì)

如圖4-2,SRAM��、MRAM和NOR FLASH的接口操作基本一致���,NIOSII的總線時(shí)序完全滿足����。故在FPGA內(nèi)部只要簡(jiǎn)單的把相應(yīng)的控制線和數(shù)據(jù)線相連就可以了,唯獨(dú)只要設(shè)計(jì)一個(gè)片選寄存器��,用來(lái)區(qū)分SIP的16個(gè)片選���。每一個(gè)片選可以訪問(wèn)的空間為128MByte��。片選寄存器的地址為(基址+0x0FFFFFFC),基地址設(shè)在NIOSII 外部總線的最高地址位����。

圖 4?2 16位SRAM/MRAM/NOR FLASH接口IP

32位SRAM/MRAM/NOR FLASH接口IP核設(shè)計(jì)

如圖4-3�����,SRAM�、MRAM和NOR FLASH的接口操作基本一致���,NIOSII的總線時(shí)序完全滿足��。故在FPGA內(nèi)部只要簡(jiǎn)單的把相應(yīng)的控制線和數(shù)據(jù)線相連就可以了��,唯獨(dú)只要設(shè)計(jì)一個(gè)片選寄存器�,用來(lái)區(qū)分SIP的16個(gè)片選。每一個(gè)片選可以訪問(wèn)的空間為128MByte���。片選寄存器的地址為(基址+0x0FFFFFFC),基地睛設(shè)在NIOSII 外部總線的最高地址位���。

圖 4?3 32位SRAM/MRAM/NOR FLASH接口IP

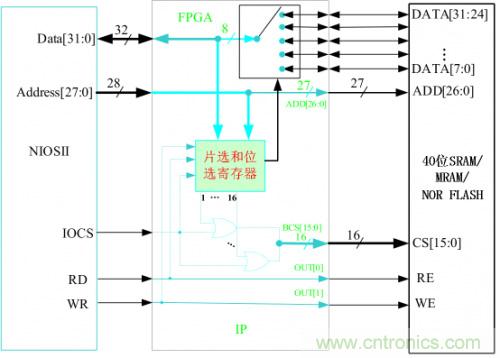

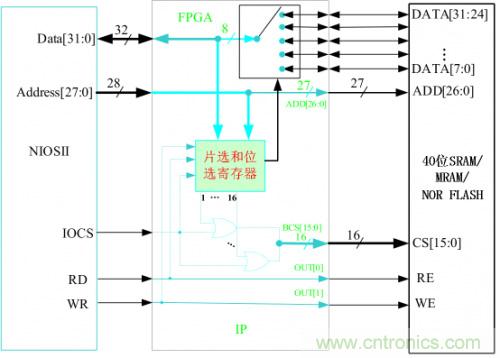

40位SRAM/MRAM/NOR FLASH接口IP核設(shè)計(jì)

如圖4-4,40位的數(shù)據(jù)寬度有點(diǎn)特殊��。在此我們把40位的數(shù)據(jù)分成5個(gè)8位的區(qū)域��,用8位寬度的總線去分別訪問(wèn)每一個(gè)區(qū)域�。IP核中的位選寄存器就是用來(lái)完成切換8位數(shù)據(jù)總線到40位總線的5個(gè)區(qū)域的其中一個(gè)。片選寄存器的地址為(基址+0x0FFFFFFC),位選寄存器的地址為(基址+0x0FFFFFF8)�。最大可以測(cè)試128M×40位×16片的存儲(chǔ)器SRAM/MRAM/NOR FLASH模塊。

圖 4?4 40位SRAM/MRAM/NOR FLASH接口IP

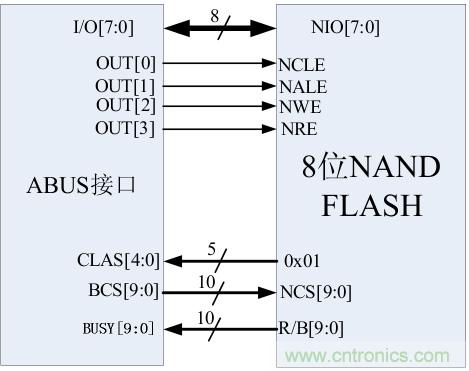

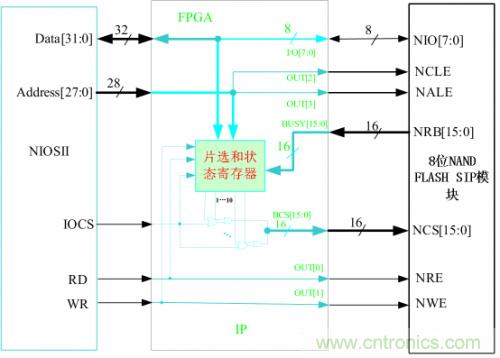

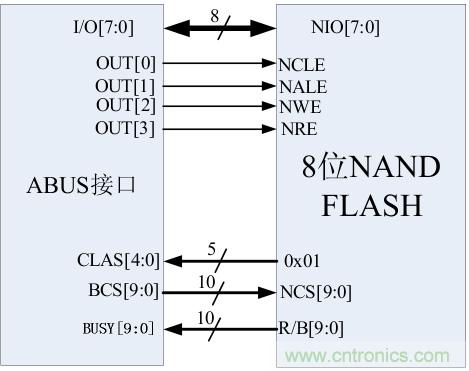

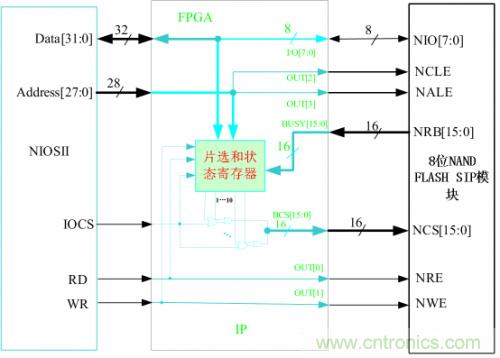

8位NAND FLASH的ABUS接口IP設(shè)計(jì)

如圖4-5����,通過(guò)寫(xiě)片選寄存器來(lái)選中模塊的16個(gè)片選的其中一個(gè)。我們約定其地址為(基址+0x0FFFFFFC)��。讀狀態(tài)寄存器返回的是16個(gè)NAND FLASH芯片的忙信號(hào)�,其地址為(基址+0x0FFFFFF8)。向地址(基址+0x00)寫(xiě)入數(shù)據(jù)就是對(duì)NAND FLASH數(shù)據(jù)寄存器的寫(xiě)操作�����。向地址(基址+0x00)單元讀數(shù)據(jù)就是對(duì)NAND FLASH數(shù)據(jù)寄存器的讀操作。向地址(基址+0x01)寫(xiě)入數(shù)據(jù)就是對(duì)NAND FLASH命令寄存器的寫(xiě)操作����。向地址(基址+0x02)寫(xiě)入數(shù)據(jù)就是對(duì)NAND FLASH地址寄存器的寫(xiě)操作。

圖 4?5 8位NAND FLASH的ABUS接口IP核設(shè)計(jì)圖

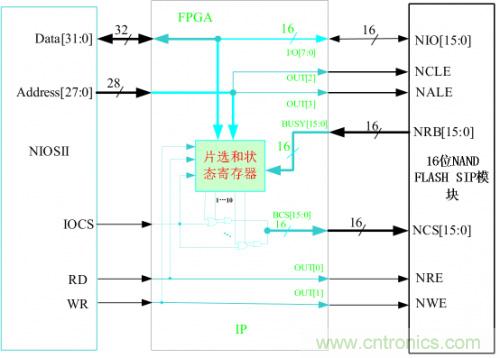

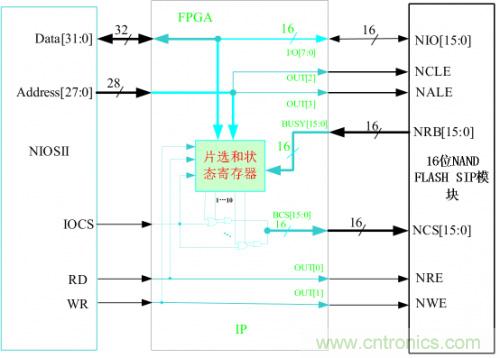

16位NAND FLASH的ABUS接口IP設(shè)計(jì)

16位的NAND FLASH存儲(chǔ)器芯片可以有多種組合方式,可以用多個(gè)16位的NAND FLASH組合,也可以用多個(gè)8位的NAND FLASH組合���。這里我們假設(shè)16位的SIP NAND FLASH產(chǎn)品是由多個(gè)16位的NAND FLASH組合而成�����,下面的IP核是根據(jù)它的結(jié)構(gòu)來(lái)設(shè)計(jì)的���。

如圖4-6,通過(guò)寫(xiě)片選寄存器來(lái)選中模塊的16個(gè)片選的其中一個(gè)��。我們約定其地址為(基址+0x0FFFFFFC)���。讀狀態(tài)寄存器返回的是16個(gè)NAND FLASH芯片的忙信號(hào),其地址為(基址+0x0FFFFFF8)�����。向地址(基址+0x00)寫(xiě)入數(shù)據(jù)就是對(duì)NAND FLASH數(shù)據(jù)寄存器的寫(xiě)操作。向地址(基址+0x00)單元讀數(shù)據(jù)就是對(duì)NAND FLASH數(shù)據(jù)寄存器的讀操作�。向地址(基址+0x01)寫(xiě)入數(shù)據(jù)就是對(duì)NAND FLASH命令寄存器的寫(xiě)操作。向地址(基址+0x02)寫(xiě)入數(shù)據(jù)就是對(duì)NAND FLASH地址寄存器的寫(xiě)操作���。

圖 4?6 16位NAND FLASH的ABUS接口IP核設(shè)計(jì)圖

驗(yàn)證與總結(jié)

將寫(xiě)好的FPGA程序和調(diào)試的C代碼寫(xiě)入FLASH后���,掉電重配置FPGA,串口的輸出能正常識(shí)別所有設(shè)置好的存儲(chǔ)器芯片�,并能夠進(jìn)行準(zhǔn)確地讀寫(xiě)功能測(cè)試。達(dá)到了設(shè)計(jì)目的�����。

本文介紹了一種低成本����、簡(jiǎn)單、靈活的多種存儲(chǔ)器芯片測(cè)試系統(tǒng)的硬件設(shè)計(jì)���,并采用FPGA�、FLASH���、SDRAM�����、RS232電路等實(shí)現(xiàn)���。采用這種方案��,用戶可根據(jù)市場(chǎng)需求�����,靈活的增加測(cè)試系統(tǒng)功能��,實(shí)現(xiàn)更多的存儲(chǔ)器芯片測(cè)試�。