【導(dǎo)讀】通常如果你的設(shè)計在較低時鐘頻率時通過了仿真,但是在較高時鐘頻率時卻失敗了,你的第一個問題應(yīng)該是你的設(shè)計在某個較高時鐘頻率時是否達(dá)到了時序約束的要求。

然而這里我們將舉這樣一個例子,就是對于某個較高時鐘頻率你已經(jīng)檢查了靜態(tài)時序分析(STA),而且時序約束也是正確的。

這種情況是什么引起的較高時鐘頻率仿真失敗呢?

可能的原因就是仿真方式、設(shè)計本身或者testbench設(shè)置方式有問題。

然而在較低時鐘頻率通過了仿真這個事實就排除了設(shè)計/testbench/仿真在設(shè)置上的問題。

排除了上面兩項,下一個可能就是脈沖拒絕(reject)或者脈沖錯誤。

“脈沖拒絕(reject)”和“脈沖錯誤”是Verilog仿真中的概念。

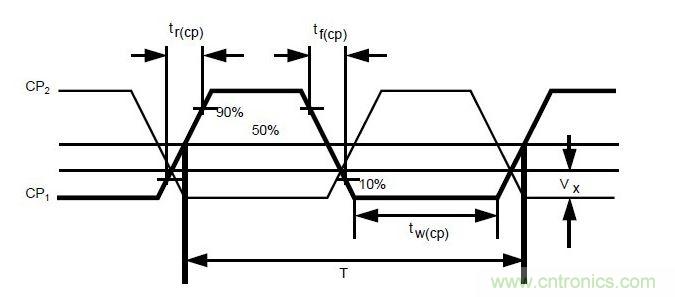

這些概念說的是脈沖的持續(xù)時間小于某個值(pulse_r)就不會通過某個電路元件。

當(dāng)然脈沖持續(xù)時間大于pulse_r,但是如果小于另一個值pulse_e盡管會通過,但是在仿真中顯示的是“x”。

這個持續(xù)時間是以通過某元器件延遲的百分比來表示的。

比如通過某元件的延遲是1ns。

0.5ns的脈沖表示為50%的持續(xù)時間。

現(xiàn)在假設(shè)設(shè)計采用的頻率是200MHz。

對應(yīng)的周期就是5ns。

那么一半就是2.5ns。

在仿真中時鐘每隔2.5ns變化一次,也就是時鐘脈沖的寬度是2.5ns。

讓我們假設(shè)內(nèi)部時鐘網(wǎng)絡(luò)某一脈沖寬度是2.8ns(也就是大于2.5ns)。

分析結(jié)果,pulse-duraTIon(脈沖持續(xù)時間)《100%。

這個脈沖可能就會被“拒絕(rejected)”,也就是說盡管時鐘信號能夠到達(dá)某個具體網(wǎng)絡(luò)的輸入端,但是卻不能從這個網(wǎng)絡(luò)輸出。

因此盡管STA分析顯示200MHz很合適,但是仿真卻不能通過。

設(shè)計其他模塊將不能獲得時鐘脈沖。

解決這個仿真問題的方法是在仿真設(shè)置中修改脈沖拒絕和錯誤(reject/error)限制。

例如在ModelSim中我們可以設(shè)置:

+transport_path_delays +transport_int_delays +pulse_r/0 +pulse_e/0

后續(xù)操作還有:

1.將pulse-rejecTIon限制修改為0。(不會拒絕任何一個脈沖)

2.將pulse-error限制修改為0。(脈沖寬度低于某個值時不會顯示輸出為“x”)

同時要將interconnect延遲模式修改為transport,其實是修改了脈沖濾波選項。

最后的問題是我們做這么多的修改就是為了能通過仿真測試嗎?

在真正的硅片中的實際情況是怎樣的?

在硅片中大部分內(nèi)部互連線在每隔幾皮秒后就會設(shè)置一個repeater(中繼器)。

因此幾納秒的脈沖會順利通過(合適的延遲),這不會存在問題。

具體出現(xiàn)問題的情形可能是這樣的:

1.頻率增加(脈沖寬度更小了)

2.器件尺寸增加(某個路徑的內(nèi)部延遲可能變大了,導(dǎo)致內(nèi)部延遲時間大于脈沖達(dá)到的傳輸時間)