【導讀】準雙向口只能有效的讀取0,而對1則是采用讀取非零的方式,就是讀入的時候要先向IO上寫1,再讀。真正的雙向口正如其名,就是真正的雙向IO不需要任何預操作可直接讀入讀出。

集電極開路(OC)

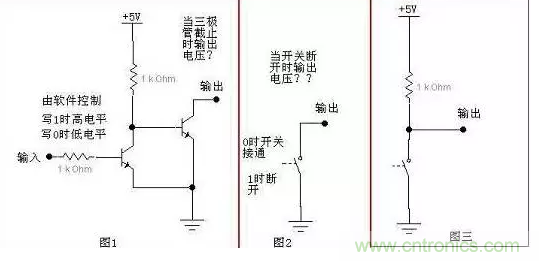

集電極開路輸出的結構如圖1所示,右邊的那個三極管集電極什么都不接,所以叫做集電極開路;左邊的三極管為反相之用,使輸入為“0”時,輸出也為“0”。對于圖 1,當左端的輸入為“0”時,前面的三極管截止,所以5v電源通過1k電阻加到右邊的三極管上,右邊的三極管導通;當左端的輸入為“1”時,前面的三極管導通,而后面的三極管截止。

我們將圖1簡化成圖2的樣子,很明顯可以看出,當開關閉合時,輸出直接接地,所以輸出電平為0。而當開關斷開時,則輸出端懸空了,即高阻態(tài)。這時電平狀態(tài)未知,如果后面一個電阻負載到地,那么輸出端的電平就被這個負載拉到低電平了,所以這個電路是不能輸出高電平的。

圖3中那個1k的電阻即是上拉電阻。如果開關閉合,則有電流從1k電阻及開關上流過,但由于開關閉和時電阻為0(方便我們的討論,實際情況中開關電阻不為0,另外對于三極管還存在飽和壓降),所以在開關上的電壓為0,即輸出電平為0。如果開關斷開,則由于開關電阻為無窮大(同上,不考慮實際中的漏電流),所以流過的電流為0,因此在1k電阻上的壓降也為0,所以輸出端的電壓就是5v了,這樣就能輸出高電平了。

但是這個輸出的內阻是比較大的 —— 即1k,如果接一個電阻為r的負載,通過分壓計算,就可以算得最后的輸出電壓為5*r/(r+1000)伏,所以,如果要達到一定的電壓的話,r就不能太小。如果r真的太小,而導致輸出電壓不夠的話,那我們只有通過減小那個1k的上拉電阻來增加驅動能力。

但是,上拉電阻又不能取得太小,因為當開關閉合時,將產生電流,由于開關能流過的電流是有限的,因此限制了上拉電阻的取值。另外還需要考慮到,當輸出低電平時,負載可能還會給提供一部分電流從開關流過,因此要綜合這些電流考慮來選擇合適的上拉電阻。

如果我們將一個讀數(shù)據(jù)用的輸入端接在輸出端,這樣就是一個IO口了,51的IO口就是這樣的結構,其中P0口內部不帶上拉,而其它三個口帶內部上拉。當我們要使用輸入功能時,只要將輸出口設置為1即可,這樣就相當于那個開關斷開,而對于P0口來說,就是高阻態(tài)了。

漏極開路(OD)

對于漏極開路(OD)輸出,跟集電極開路輸出是十分類似的。將上面的三極管換成場效應管即可。這樣集電極就變成了漏極,OC就變成了OD,原理分析是一樣的。OC門主要用于3個方面:實現(xiàn)與或非邏輯,用做電平轉換,用做驅動器。

開漏形式的電路有以下幾個特點:

利用外部電路的驅動能力,減少IC內部的驅動,或驅動比芯片電源電壓高的負載。

可以將多個開漏輸出的Pin,連接到一條線上。通過一只上拉電阻,在不增加任何器件的情況下,形成“與邏輯”關系。這也是I2C,SMBus等總線判斷總線占用狀態(tài)的原理。

由于漏級開路,所以后級電路必須接一上拉電阻,上拉電阻的電源電壓就可以決定輸出電平。這樣就可以進行任意電平的轉換了。

源極開路提供了靈活的輸出方式,但是也有其弱點,就是帶來上升沿的延時。因為上升沿是通過外接上拉無源電阻對負載充電,所以當電阻選擇小時延時就小,但功耗大;反之延時大功耗小。所以如果對延時有要求,則建議用下降沿輸出。

推挽輸出

另一種輸出結構是推挽輸出。推挽輸出的結構就是把上面的上拉電阻也換成一個開關,當要輸出高電平時,上面的開關通,下面的開關斷;而要輸出低電平時,則剛好相反。

比起OC或者OD來說,這樣的推挽結構高、低電平驅動能力都很強。如果兩個輸出不同電平的輸出口接在一起的話,就會產生很大的電流,有可能將輸出口燒壞。而上面說的OC或OD輸出則不會有這樣的情況,因為上拉電阻提供的電流比較小。如果是推挽輸出的要設置為高阻態(tài)時,則兩個開關必須同時斷開(或者在輸出口上使用一個傳輸門),這樣可作為輸入狀態(tài),AVR單片機的一些IO口就是這種結構。

驅動電路的兩種形式:

單片機內部的邏輯經過內部的邏輯運算后需要輸出到外面,外面的器件可能需要較大的電流才能推動,因此在單片機的輸出端口必須有一個驅動電路。

采用一只N型三極管

其中的一種是采用一只N型三極管 —— NPN或N溝道,以NPN三極管為例,就是e接地,b接內部的邏輯運算,c引出。b受內部驅動可以控制三極管是否導通,但如果三極管的c極一直懸空,盡管b極上發(fā)生高低變化,c極上也不會有高低變化,因此在這種條件下必須在外部提供一個電阻,電阻的一端接c(引出腳)另一端接電源,這樣當三極管的b有高電壓是三極管導通,c電壓為低,當b為低電壓時三極管不通,c極在電阻的拉動下為高電壓。

這種驅動電路有個特點:低電壓是三極管驅動的,高電壓是電阻驅動的——上下不對稱,三極管導通時的ec內阻很小,因此可以提供很大的電流,可以直接驅動led甚至繼電器,但電阻的驅動是有限的,最大高電平輸出電流=(VCC-Vh)/r。

采用兩只晶體管

另一種是互補推挽輸出,采用兩只晶體管,一只在上一只在下,上面的一只是n型,下面為p型(以三極管為例),兩只管子的連接為:NPN(上)的c連VCC,PNP(下)的c接地,兩只管子的ee,bb相連,其中ee作為輸出(引出腳),bb接內部邏輯。這個電路通常用于功率放大點路的末級(音響),當bb接高電壓時NPN管導通輸出高電壓,由于三極管的ec電阻很小,因此輸出的高電壓有很強的驅動能力,當bb接低電壓時NPN截至,PNP導通,由于三極管的ec電阻很小因此輸出的低電壓有很強的驅動能力。

簡單的例子,9013導通時ec電阻不到10歐,以Vh=2.5v,VCC=5v計算,高電平輸出電流最大=250MA,短路電流500ma,這個計算同時告訴我們采用推挽輸出時一定要小心千萬不要出現(xiàn)外部電路短路的可能,否則肯定燒毀芯片,特別是外部驅動三極管時別忘了在三極管的基極加限流電阻。推挽輸出電路的形式很多,有些單片機上下都采用n型管,但內部邏輯提供互補輸出,以上的說明僅僅為了說明推挽的原理,為了更深的理解可以參考功率放大電路。

上拉電阻和弱上拉

上拉電阻很大,提供的驅動電流很小叫弱上拉,反之叫強上拉。

為什么要使用拉電阻:

上拉就是將不確定的信號通過一個電阻嵌位在高電平,電阻同時起限流作用,下拉同理。上拉是對器件注入電流,下拉是輸出電流,弱強只是上拉電阻的阻值不同,沒有什么嚴格區(qū)分。

對于非OC、OD輸出型電路提升電流和電壓的能力是有限的,上拉電阻的功能主要是為集電極開路輸出型電路輸出電流通道。

上拉電阻的主要應用:

當TTL電路驅動COMS電路時,如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V),這時就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。

OC門電路要輸出“1”時需要加上拉電阻,不加根本就沒有高電平。

為加大輸出引腳的驅動能力,有的單片機管腳上也常使用上拉電阻,但在用OC門作驅動(例如:控制一個 LED)灌電流工作時就可以不加上拉電阻。

在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產生降低輸入阻抗,提供泄荷通路。

提高總線的抗電磁干擾能力。管腳懸空就比較容易接受外界的電磁干擾。

長線傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。

上拉電阻阻值的選擇原則包括:

從節(jié)約功耗及芯片的灌電流能力考慮應當足夠大;電阻大,電流小。

從確保足夠的驅動電流考慮應當足夠??;電阻小,電流大。

對于高速電路,過大的上拉電阻可能邊沿變平緩。

綜合考慮以上三點,通常在1k到10k之間選取。對下拉電阻也有類似道理。

三態(tài)門

高阻態(tài)時引腳對地電阻無窮,此時讀引腳電平時可以讀到真實的電平值。高阻態(tài)的重要作用就是I/O(輸入/輸出)口在輸入時讀入外部電平用。一般門與其它電路的連接,無非是兩種狀態(tài),1或者0,在比較復雜的系統(tǒng)中,為了能在一條傳輸線上傳送不同部件的信號,研制了相應的邏輯器件稱為三態(tài)門。

三態(tài)門,除了有這兩種狀態(tài)以外還有一個高阻態(tài),就是高阻抗(電阻很大,相當于開路)。相當于該門與和它連接的電路處于斷開的狀態(tài)。三態(tài)門是一種擴展邏輯功能的輸出級,也是一種控制開關。

主要是用于總線的連接,因為總線只允許同時只有一個使用者。通常在數(shù)據(jù)總線上接有多個器件,每個器件通過OE/CE之類的信號選通。如器件沒有選通的話它就處于高阻態(tài),相當于沒有接在總線上,不影響其它器件的工作。

準雙向口

準雙向口只能有效的讀取0,而對1則是采用讀取非零的方式,就是讀入的時候要先向IO上寫1,再讀。真正的雙向口正如其名,就是真正的雙向IO不需要任何預操作可直接讀入讀出。