【導(dǎo)讀】伴隨著5G通信技術(shù)的到來(lái)與越來(lái)越成熟的物聯(lián)網(wǎng)技術(shù)的應(yīng)用,人們對(duì)5G/IoT相關(guān)的集成電路芯片設(shè)計(jì)投來(lái)更加熱切的目光。針對(duì)5G/IoT技術(shù)的迫切需求,本文介紹集成電路產(chǎn)業(yè)中版圖設(shè)計(jì)技術(shù)的簡(jiǎn)要過(guò)程��,從而講述標(biāo)準(zhǔn)版圖設(shè)計(jì)��、半定制設(shè)計(jì)與全定制版圖設(shè)計(jì)的應(yīng)用���,并以5G/IoT場(chǎng)合的高性能和高速數(shù)據(jù)率相關(guān)的IP進(jìn)行簡(jiǎn)短的討論��,版圖設(shè)計(jì)質(zhì)量對(duì)最終系統(tǒng)的影響等����。

同時(shí)���,云端大數(shù)據(jù)的數(shù)據(jù)流實(shí)時(shí)處理(real-time analytical processing)推動(dòng)著高性能計(jì)算機(jī)芯片的研發(fā)�����;終端的存儲(chǔ)一體化運(yùn)算(in-memory computing��,IMC)對(duì)新一代存儲(chǔ)器單元設(shè)計(jì)有了更新的要求����。無(wú)論是云端或是終端的芯片設(shè)計(jì),當(dāng)前與未來(lái)都要具有人工智能的機(jī)器學(xué)習(xí)功能����,云端芯片更多地解決并提升深度學(xué)習(xí)中的“訓(xùn)練”(training)能力, 終端芯片則更多地解決并提升深度學(xué)習(xí)中的“推理”(inference)能力。

5G/IoT的專用集成電路的市場(chǎng)需求��,云端終端的智能芯片發(fā)展要求�,從架構(gòu)到系統(tǒng),包括電路設(shè)計(jì)與物理設(shè)計(jì)與版圖設(shè)計(jì)項(xiàng)目���,已經(jīng)擺在了芯片設(shè)計(jì)團(tuán)隊(duì)的面前�。這些設(shè)計(jì)包括了集成電路的標(biāo)準(zhǔn)設(shè)計(jì)���、半定制設(shè)計(jì)和全定制設(shè)計(jì)�。芯片制造商通常僅提供通用型單元庫(kù)(generic library)因而IoT需要更多半定制����、5G需要全定制的版圖設(shè)計(jì)��。

針對(duì)5G/IoT技術(shù)的迫切需求��,本文介紹集成電路產(chǎn)業(yè)中版圖設(shè)計(jì)技術(shù)的簡(jiǎn)要過(guò)程����,從而講述標(biāo)準(zhǔn)版圖設(shè)計(jì)��、半定制設(shè)計(jì)與全定制版圖設(shè)計(jì)的應(yīng)用��,并以5G/IoT場(chǎng)合的高性能和高速數(shù)據(jù)率相關(guān)的IP進(jìn)行簡(jiǎn)短的討論�,版圖設(shè)計(jì)質(zhì)量對(duì)最終系統(tǒng)的影響等�����。文末強(qiáng)調(diào)版圖設(shè)計(jì)與系統(tǒng)芯片����、MCU芯片與模擬和混合信號(hào)設(shè)計(jì)以及與射頻芯片設(shè)計(jì)的緊密相關(guān)和依賴性,重點(diǎn)說(shuō)明版圖設(shè)計(jì)在集成電路產(chǎn)業(yè)中的重要角色����。

1. 集成電路的版圖設(shè)計(jì)方法

集成電路設(shè)計(jì)方法涉及面廣,內(nèi)容復(fù)雜����,其中版圖設(shè)計(jì)是集成電路物理實(shí)現(xiàn)的基礎(chǔ)技術(shù)。版圖設(shè)計(jì)的質(zhì)量好壞直接會(huì)影響到集成電路的功耗�����、性能和面積。在系統(tǒng)芯片(system-on-chip, SoC)設(shè)計(jì)中����,集成了接口單元(input/output,I/O),標(biāo)準(zhǔn)邏輯單元(standard cell),模擬與混合信號(hào)(analog mixed-signal, AMS)模塊����,存儲(chǔ)器(memory,例如ROM,RAM)和多種IP模塊。所有這些模塊的物理實(shí)現(xiàn),全都離不開(kāi)基本的版圖設(shè)計(jì)���。

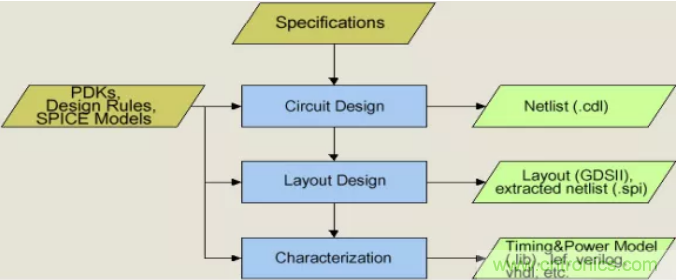

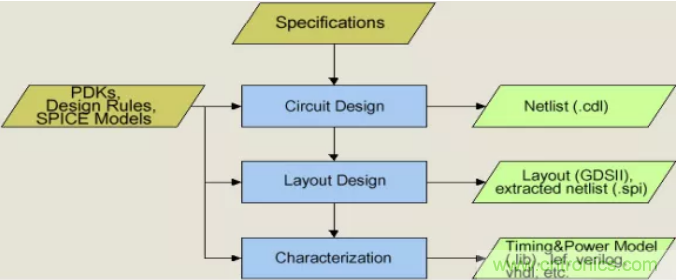

工程實(shí)踐中���,從定義系統(tǒng)芯片參數(shù)(specifications)完成后,人們常常將最常見(jiàn)的數(shù)字集成電路中標(biāo)準(zhǔn)邏輯單元的版圖設(shè)計(jì)過(guò)程簡(jiǎn)化為電路設(shè)計(jì)(circuit design)��、版圖設(shè)計(jì)(layout design)和特征化(characterization)等三個(gè)步驟����,見(jiàn)圖1簡(jiǎn)化的版圖設(shè)計(jì)流程圖。在實(shí)踐中���,版圖設(shè)計(jì)類型又分為: 1)標(biāo)準(zhǔn)版圖設(shè)計(jì),2)半定制版圖設(shè)計(jì)�,和3)全定制版圖設(shè)計(jì)��。

圖1 集成電路版圖設(shè)計(jì)的簡(jiǎn)化流程圖

2.集成電路中的標(biāo)準(zhǔn)版圖設(shè)計(jì)

標(biāo)準(zhǔn)版圖設(shè)計(jì)通常用于數(shù)字集成電路的標(biāo)準(zhǔn)單元庫(kù)���、輸入輸出單元庫(kù)等。存儲(chǔ)器的版圖設(shè)計(jì)屬于半定制版圖設(shè)計(jì)����,它的存儲(chǔ)單元(例如RAM cell)的版圖采用標(biāo)準(zhǔn)單元庫(kù)的設(shè)計(jì)方法,其余部分則為不規(guī)則的版圖設(shè)計(jì)。模擬與混合信號(hào)(analog mixed-signal, AMS)的版圖設(shè)計(jì)以及射頻電路的版圖設(shè)計(jì)則屬于全定制的版圖設(shè)計(jì)�。

標(biāo)準(zhǔn)單元庫(kù)中包括兩大類單元:(1)組合邏輯(combinational)單元,例如反向器與非門(mén)、選擇器等���。(2)時(shí)序邏輯(sequential)單元���,例如寄存器、鎖存器����、存儲(chǔ)器等。

對(duì)于數(shù)字電路中的標(biāo)準(zhǔn)單元設(shè)計(jì)���,是從布爾邏輯(Boolean logic)描述并定義單元的邏輯關(guān)系開(kāi)始����,接著是電路設(shè)計(jì)(schematic capture或circuit design)與電路仿真(circuit simulation),而后開(kāi)始版圖設(shè)計(jì)�。版圖設(shè)計(jì)需要符合制造工藝規(guī)則檢查(design rule check,DRC)和版圖電路一致性檢查(layout versus schematic�,LVS)通過(guò)才算完成,這時(shí)���,版圖設(shè)計(jì)的結(jié)果用“圖形顯示系統(tǒng)第二版”(graphic display system II�,GDSII)文件記載�����,并作為芯片制造中制作掩模板(mask)的依據(jù)���。數(shù)字電路的標(biāo)準(zhǔn)單元和I/O單元完成版圖設(shè)計(jì)后��,還要做寄生參數(shù)(電阻R電容C)提?����。╬arasitic extraction��,RCX),供電路設(shè)計(jì)者作進(jìn)一步擬合優(yōu)化處理����,這種反標(biāo)方法(back-annotation)也是芯片級(jí)設(shè)計(jì)的重要步驟之一。圖2給出了比較完整的版圖設(shè)計(jì)全流程圖����。

圖2 集成電路版圖設(shè)計(jì)的全流程圖

從標(biāo)準(zhǔn)單元和I/O單元的版圖設(shè)計(jì)結(jié)果�,需要產(chǎn)生物理信息和時(shí)序信息供芯片物理設(shè)計(jì)布局布線(place & route,P&R)使用�����。物理信息以單元庫(kù)交換格式(library exchange format����,LEF)文件表達(dá),它是在相應(yīng)的GDSII文件的基礎(chǔ)上�����,“忽略”底層信息����,僅僅保留并提取金屬1層(metal 1,M1)以及更上層的多邊形(polygon)數(shù)據(jù)作為P&R使用��,這樣就會(huì)極大地加快P&R的運(yùn)行速度,縮短時(shí)序收斂時(shí)間��。例如����,對(duì)于存儲(chǔ)器版圖的LEF文件,會(huì)使用到M1���,M2甚至M3的信息���。

圖3 集成電路標(biāo)準(zhǔn)版圖設(shè)計(jì)中標(biāo)準(zhǔn)單元具有同等高度與不同寬度

對(duì)于標(biāo)準(zhǔn)單元的版圖,根據(jù)工藝要求���,標(biāo)準(zhǔn)邏輯單元的高度是固定的���,寬度為最小單元寬度的公約數(shù)倍數(shù),例如在圖3中�,左圖為反向器(inverter,INV)的版圖����,中圖為選擇器(multiplexer,MUX)的版圖��,右圖為D型寄存器的(D-Flip Flop, DFF)的版圖。如上所述�����,從版圖設(shè)計(jì)中����,可以導(dǎo)出并建立GDSII和LEF文件�。GDSII文件經(jīng)過(guò)設(shè)計(jì)簽核(design sign-off)過(guò)程由代工廠使用于芯片制造,LEF文件用于全芯片的P&R物理設(shè)計(jì)���。

標(biāo)準(zhǔn)單元的時(shí)序信息過(guò)去曾經(jīng)以時(shí)序庫(kù)單元格式(timing library format�,TLF)文件表達(dá)����,目前以自由時(shí)序庫(kù)單元格式(liberty,“.lib”)文件表達(dá)�。產(chǎn)生時(shí)序庫(kù)文件需要根據(jù)制造工藝調(diào)用SPICE模型,比如最常用的BISM4模型�;根據(jù)制造工藝參數(shù),進(jìn)行庫(kù)單元時(shí)序仿真��,例如Hspice和Spectre仿真器�。

從相應(yīng)的GDSII文件中��,根據(jù)半導(dǎo)體器件物理基礎(chǔ)參數(shù)���,提取單元電路的輸入輸出負(fù)載(CL),提取其靜態(tài)功耗和動(dòng)態(tài)功耗數(shù)據(jù)��,建立一套數(shù)據(jù)庫(kù)����,在做功耗分析和低功耗設(shè)計(jì)時(shí)使用。CMOS的總功耗 Ptotal= Pstatic + Pdynamic�����,靜態(tài)功耗Pstatic與工藝參數(shù)相關(guān)�,而動(dòng)態(tài)功耗Pdynamic與CL相關(guān)。因此��,在做各種版圖設(shè)計(jì)時(shí)����,應(yīng)當(dāng)盡量減小輸入輸出端的電容,從而提高庫(kù)單元速度即芯片的性能��。

另一方面�����,對(duì)于180nm或者更加先進(jìn)的工藝,信號(hào)完整性(signal integrity, SI)分析成為必不可少的步驟�。人們知道,在CMOS電路的翻轉(zhuǎn)過(guò)程除了受信號(hào)上升或下降時(shí)間(transition time,也稱作slew rate)快慢有關(guān)之外,與其柵極的閾值(threshold voltage)極其相關(guān)��。當(dāng)輸出輸入電壓的斜率達(dá)到1時(shí)���,即|tan(Vout/Vin)|=1(該點(diǎn)稱作統(tǒng)一增益點(diǎn)�����,Unity Gain Point,UGP)�����,若有臨近的并行信號(hào)線通過(guò)電容耦合(coupling capacitance)產(chǎn)生“噪聲(noise)”信號(hào)與“受害者”的時(shí)鐘或者數(shù)據(jù)信號(hào)迭加����,就會(huì)破壞正常數(shù)據(jù)信號(hào)的傳遞甚或使得設(shè)計(jì)失效。

如此可見(jiàn)�����,標(biāo)準(zhǔn)單元的版圖設(shè)計(jì)結(jié)果是產(chǎn)生時(shí)序單元格式文件的來(lái)源。由于單元延時(shí)與信號(hào)輸入端的翻轉(zhuǎn)時(shí)間tslew(transition time)以及負(fù)載(CL)相關(guān)����,因此,時(shí)序單元格式文件中的延時(shí)函數(shù)為f(tslew�����,CL),用三維表格表示�,兩個(gè)數(shù)據(jù)之間的中間值使用多項(xiàng)式(polynomial)簡(jiǎn)化插值方法產(chǎn)生,供計(jì)算時(shí)序時(shí)使用���。另一方面�,標(biāo)準(zhǔn)單元的功耗信息和信號(hào)完整性信息函數(shù)同樣與(tslew��,CL)相關(guān),也用三維表格表示��。時(shí)序單元文件的時(shí)序�、功耗和SI等豐富信息,將用于全芯片物理設(shè)計(jì)過(guò)程中的靜態(tài)時(shí)序分析(static timing analysis�����,STA)、功耗分析和信號(hào)完整性分析����。芯片代工廠(foundry)通常只提供通用型GP (general purpose) 單元庫(kù),例如TSMC從40nm及以下工藝才開(kāi)始提供低功耗(LP)單元庫(kù)和超低功耗(ULP)單元庫(kù)。若采用65nm及以上的工藝,用戶應(yīng)當(dāng)自行設(shè)計(jì),并且產(chǎn)生完整的單元庫(kù)文件GDSII, LEF 和 “.lib” 等�����。

在版圖設(shè)計(jì)中人們可以使用工藝設(shè)計(jì)包(process design kit, PDK),或者稱作 “工藝設(shè)計(jì)錦囊”����,這當(dāng)然給版圖設(shè)計(jì)帶來(lái)了極大的便利。但是�,在很多工程設(shè)計(jì)中,人們還是離不開(kāi)很多基礎(chǔ)設(shè)計(jì)步驟。例如���,參數(shù)化的標(biāo)準(zhǔn)單元(parameterized cell,Pcell)可以幫助工程人員直接定義CMOS晶體管的大小并且直接調(diào)用�,在28nm或者更先進(jìn)工藝條件下,還需要考慮制造誤差比如光學(xué)臨近誤差(optical proximity correction, OPC)等帶來(lái)的影響�,對(duì)版圖設(shè)計(jì)進(jìn)行校正。

3.集成電路中的半定制版圖設(shè)計(jì)

在半定制版圖設(shè)計(jì)中�,例如具有6個(gè)晶體管的SRAM或者僅有1個(gè)晶體管1個(gè)電容的DRAM,它們的標(biāo)準(zhǔn)小單元(RAM cell)高度和寬度尺寸設(shè)置與上一節(jié)所說(shuō)的標(biāo)準(zhǔn)邏輯單元無(wú)關(guān)�����,需要單獨(dú)設(shè)計(jì),見(jiàn)圖4�。這一類設(shè)計(jì)既要兼顧標(biāo)準(zhǔn)版圖設(shè)計(jì)的通用性,又要考慮到重復(fù)使用單元在當(dāng)前模塊設(shè)計(jì)中使用的靈活性。早期英特爾公司的CPU芯片的設(shè)計(jì)就采用了很多半定制的版圖設(shè)計(jì)����,這種版圖設(shè)計(jì)技巧也會(huì)用于高性能計(jì)算機(jī)芯片的CPU設(shè)計(jì)之中。比如CPU中的數(shù)據(jù)通道(datapath)部分如果使用標(biāo)準(zhǔn)單元����,則往往成為實(shí)現(xiàn)高性能的瓶頸,而采用半定制的專門(mén)設(shè)計(jì)����,才會(huì)更好地提高整個(gè)芯片的性能。

圖4 半定制版圖設(shè)計(jì)中重復(fù)使用的RAM單元具有不同高度與不同寬度

(從左往右: 6T-SRAM單元電路及其版圖, 1T1C-DRAM單元電路及其版圖)

還有一類特殊的半定制版圖稱為客戶自有技術(shù)(Custom-Owned Tooling����,COT)模塊,在專用集成電路(application specific integrated circuit����,ASIC)中經(jīng)常采用。閃存存取器(flash memory)的基本單元(NAND和NOR單元)與上述SRAM和DRAM的基本單元類似�,也是采用半定制版圖設(shè)計(jì)。眾所周知,NAND閃存已經(jīng)廣泛用于新型的固態(tài)存儲(chǔ)器(solid state drive, SSD)中。目前,數(shù)字電路基本單元常常工作在幾百兆赫茲(MHz)的頻率���。DRAM新一代產(chǎn)品��,即先進(jìn)的雙數(shù)據(jù)率同步動(dòng)態(tài)存儲(chǔ)器(double data rate synchronous dynamic RAM, DDR SDRAM)系列(最新版本為DDR4)和LPDDR系列(最新版本LPDDR5)數(shù)據(jù)率達(dá)到了6.4Gbps)�����,可以廣泛用于5G通信和汽車電子的芯片設(shè)計(jì)中����。

上面討論到��,Pcell可以幫助工程人員直接定義CMOS晶體管的大小���,可以直接調(diào)用或者方便地更換從而對(duì)設(shè)計(jì)不斷進(jìn)行優(yōu)化���。在28nm或者更先進(jìn)工藝條件下,尤其是模擬電路對(duì)工藝參數(shù)根據(jù)敏感并直接影響到性能�。這些問(wèn)題可以通過(guò)約束控制設(shè)計(jì)(constraint-driven design, CDD)方法加以克服��。比如,在進(jìn)行差分對(duì)晶體管設(shè)計(jì)時(shí)��,工程人員可以調(diào)用約束文件,對(duì)差分對(duì)電路進(jìn)行控制配對(duì)�����,實(shí)現(xiàn)預(yù)定的性能��。

與標(biāo)準(zhǔn)時(shí)序單元相比,存儲(chǔ)器的時(shí)序關(guān)系比較復(fù)雜�����。通常前者主要關(guān)注“時(shí)鐘(CLK_)”與“數(shù)據(jù)(DATA_)”信號(hào)之間的建立(setup)時(shí)間和(hold)時(shí)間; 后者還要額外處理“地址(ADD_)”�����、“控制(CONTR_)”�����、“讀(RE_)” �、“寫(xiě)(WR_)” 、“使能(EN_)”等信號(hào)關(guān)系����。

熟練地掌握了標(biāo)準(zhǔn)單元版圖設(shè)計(jì)之后,對(duì)于半定制版圖設(shè)計(jì)方能駕輕就熟����,舉一反三����,并借助CDD方法����,很好地處理設(shè)計(jì)規(guī)則并符合工藝制造的要求。一般說(shuō)來(lái)����,數(shù)字電路的標(biāo)準(zhǔn)單元或者其他電路設(shè)計(jì)由前端(front-end)工程師完成;版圖設(shè)計(jì)則由后端(back-end)工程師完成��。在模擬和混合信號(hào)模塊或者芯片設(shè)計(jì)中�,電路設(shè)計(jì)與版圖設(shè)計(jì)溶為一體,才能達(dá)到更好的性能要求�。

4.集成電路中的全定制版圖設(shè)計(jì)

在模擬和混合信號(hào)芯片設(shè)計(jì)中,更多地采用了全定制版圖設(shè)計(jì)方法;尤其是射頻電路的芯片設(shè)計(jì)���,基本上必須通過(guò)全定制版圖設(shè)計(jì)來(lái)實(shí)現(xiàn)�����,這樣才能有效地達(dá)到電路的設(shè)計(jì)目標(biāo)��,比如�,信號(hào)耦合與匹配��,有源區(qū)器件和無(wú)源區(qū)器件的實(shí)現(xiàn)����,高頻參數(shù)電感和自感參數(shù)的控制和優(yōu)化等。

模擬和混合信號(hào)芯片設(shè)計(jì)包括常見(jiàn)的模擬前端控制器(analog front-end, AFE)����、模數(shù)轉(zhuǎn)換器(analog-digital converter, ADC)、數(shù)模轉(zhuǎn)換器(digital-analog converter, DAC)��、運(yùn)算放大器(op-amp)和比較器(comparator)等�。

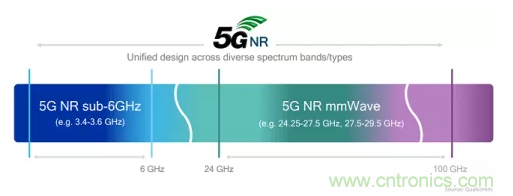

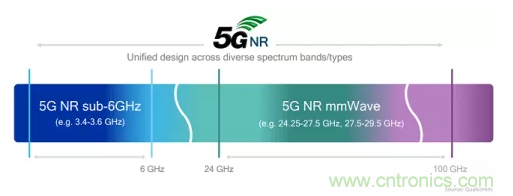

5G通信采用的頻段規(guī)范稱作“5G新空口”(5G New Radio,5G NR),使用6 GHz以下頻率以及毫米波波段,見(jiàn)圖5��。數(shù)據(jù)率為10~20Gbps

圖5 5G NR頻率和5G NR毫米波頻率范圍

射頻無(wú)線通信技術(shù)包括蜂鳥(niǎo)(ZigBee���,IEEE 802.15.4)����,無(wú)線(WiFi,2.4GHz/5GHz,IEEE 802.11)����,藍(lán)牙(最新版本Bluetooth 5.0, 2.4~2.483.5GHz)和藍(lán)牙低功耗(Bluetooth Low Energy�,BLE, SIG/IEEE 802.15.1)和全球互通微波訪問(wèn)(WiMax, 3.5~5.8GHz, IEEE 802.16d; 2.3,2.5,3.5GHz,IEEE 802.16e)等5種標(biāo)準(zhǔn)�。與這些通信技術(shù)相關(guān)的射頻芯片設(shè)計(jì)包括IoT常用的接口,例如串并聯(lián)接口(Serial Parallel Interface���,SPI)模塊���,射頻功率放大器(RF PA),低噪聲放大器(low noise amplifier�,LNA),壓控振蕩器(voltage-controlled oscillator, VCO)�����,混頻器(frequency mixer)��,濾波器(filter)等�。

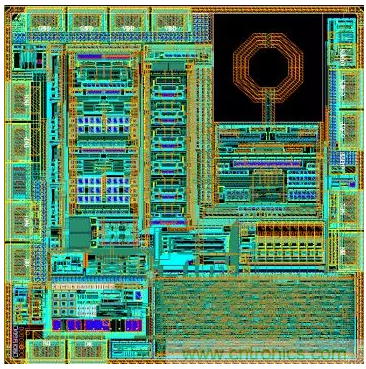

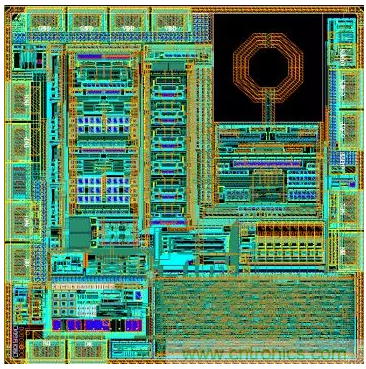

射頻無(wú)線模塊或者獨(dú)立的射頻芯片,從電路設(shè)計(jì)到版圖設(shè)計(jì),完全屬于全定制設(shè)計(jì)方式。設(shè)計(jì)人員在標(biāo)準(zhǔn)版圖設(shè)計(jì)和半定制版圖設(shè)計(jì)的基礎(chǔ)上,不斷開(kāi)發(fā)出專用的芯片射頻產(chǎn)品����。圖6為某射頻公司自行設(shè)計(jì)的5GHz通信產(chǎn)品全定制版圖案例,即版圖為全手工設(shè)計(jì),芯片制造采用180nm射頻工藝,其數(shù)據(jù)率達(dá)到5Gbps。

圖6 某射頻公司5Gbps通信產(chǎn)品全定制(手工)版圖設(shè)計(jì)案例

藍(lán)牙芯片產(chǎn)品開(kāi)發(fā)相對(duì)比較困難����,射頻的性能與功耗是衡量藍(lán)牙芯片的重要指標(biāo)�����,包括數(shù)據(jù)傳輸速率、信號(hào)延時(shí)與穩(wěn)定性等都是芯片開(kāi)發(fā)與研究的挑戰(zhàn)�。包括采用40nm的CMOS藍(lán)牙芯片的亞閾值建模與電路仿真,版圖后仿真與優(yōu)化等��。目前����,不少射頻應(yīng)用芯片已經(jīng)向40nm以下的先進(jìn)工藝開(kāi)發(fā),這時(shí),設(shè)計(jì)人員需要器件建模(例如BSIM6仿真模型)和全定制版圖設(shè)計(jì)雙管齊下。

熟練地掌握了標(biāo)準(zhǔn)單元版圖設(shè)計(jì)和半定制版圖設(shè)計(jì)之后����,對(duì)于全定制版圖設(shè)計(jì)方能駕輕就熟,運(yùn)用自如��,以CDD方法加以輔助�����,則更好地處理模擬混合信號(hào)和射頻設(shè)計(jì)規(guī)則的特殊要求�����,例如電感和互感對(duì)版圖的影響,及其工藝制造后的實(shí)測(cè)結(jié)果�����。

5.高性能與高速芯片設(shè)計(jì)與版圖設(shè)計(jì)

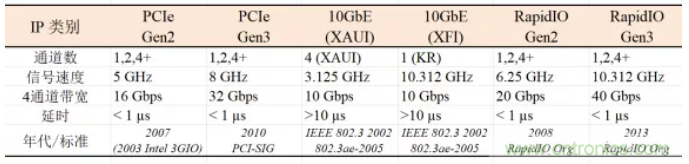

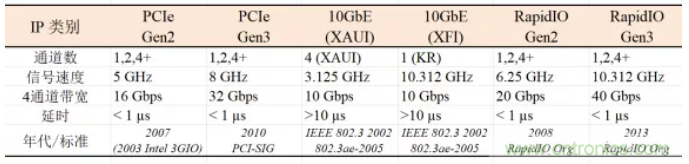

物聯(lián)網(wǎng)和5G聯(lián)網(wǎng)通信中除了信號(hào)收發(fā)單元(transceiver, TRX 以及TX/RX)設(shè)計(jì)芯片之外,離不開(kāi)專用的系統(tǒng)芯片SoC,其中高性能與高速核心IP往往決定了SoC的性能和速度����。常見(jiàn)的高性能與高速核心IP有: PCIe, 10 Gigabit Ethernet (10 GbE), RapidIO, SerDes, USB等。表1列出了幾種物聯(lián)網(wǎng)和5G時(shí)代常用的高性能與高速I(mǎi)P的信號(hào)速度和數(shù)據(jù)率�。

第1代PCIe總線技術(shù)最早于2003年提出,它源自英特爾公司的第3代輸入輸出3GIO技術(shù)。2017年P(guān)CIe第4代提出,2019年將開(kāi)發(fā)PCIe第5代�����。英偉達(dá)公司注重機(jī)器學(xué)習(xí)中數(shù)據(jù)處理GPU芯片的開(kāi)發(fā),目前采用PCIe第2代產(chǎn)品,已經(jīng)實(shí)現(xiàn)了16Gbps數(shù)據(jù)率����。

高速I(mǎi)P接口吉比特以太網(wǎng)10GbE (IEEE 820.3ae-2002)采用全工協(xié)議(full-duplex protocol),用來(lái)處理以太網(wǎng)的高數(shù)據(jù)率數(shù)據(jù),廣泛用于需要高帶寬的企業(yè)服務(wù)器和數(shù)據(jù)中心等, 表1列出了10GbE (連接MAC層和PHY層的)的兩種接口參數(shù),即4通道XAUI模式和單通道XFI/KR模式。

RapidIO用來(lái)作為與處理器之間的信號(hào)互聯(lián),大量用在數(shù)據(jù)中心和高性能計(jì)算機(jī)嵌入式芯片設(shè)計(jì)中,也用于異構(gòu)系統(tǒng)(heterogeneous system architecture, HSA)芯片中,包括人工智能芯片采用的CPU,DSP,GPU等設(shè)計(jì)�����。

表1 物聯(lián)網(wǎng)和5G常用IP模塊的信號(hào)速度和數(shù)據(jù)率比較

由上表可見(jiàn),使用高速I(mǎi)P時(shí)離不開(kāi)相關(guān)IP設(shè)計(jì)的控制器(Controller)模塊和物理層(PHY)模塊的設(shè)計(jì),它們必須滿足3~10GHz信號(hào)頻率要求,相應(yīng)的數(shù)據(jù)率10~40Gbps對(duì)于芯片的版圖設(shè)計(jì)充滿了技術(shù)挑戰(zhàn)。

6.當(dāng)代及未來(lái)5G/IoT應(yīng)用對(duì)版圖設(shè)計(jì)技術(shù)影響

針對(duì)高端數(shù)字芯片的性能要求,設(shè)計(jì)公司為了滿足需求,會(huì)專門(mén)投入研發(fā)人員,重新對(duì)標(biāo)準(zhǔn)單元庫(kù)進(jìn)行電路優(yōu)化和版圖設(shè)計(jì),如第2小節(jié)中“標(biāo)準(zhǔn)版圖設(shè)計(jì)”所說(shuō),還要重新產(chǎn)生一套單元庫(kù)文件,包括GDSII, LEF和 “.lib”等�����。對(duì)于半定制設(shè)計(jì)版圖,比如COT模塊等,除了注意邊界處的走線,也要產(chǎn)生“灰盒子”時(shí)序文件��。IoT相關(guān)芯片以MCU為主的SoC, 其中若干種IP模塊和無(wú)線模塊包括NB-IoT, LoRa, 藍(lán)牙等, 給半定制和全定制版圖設(shè)計(jì)帶來(lái)新的生命�����。5G時(shí)代的應(yīng)用場(chǎng)景有三種不同的無(wú)線接入模式�,包括以消費(fèi)類為主的增強(qiáng)移動(dòng)寬帶(enhanced Mobile Broadband, eMBB)技術(shù)�,以智慧機(jī)器人和無(wú)人駕駛等為主的超高可靠超低時(shí)延通信(Ultra-reliable low latency communication, URLLC)和大規(guī)模機(jī)器通信(massive Machine‐Type Communication, mMTC)。這些多樣化的應(yīng)用場(chǎng)景會(huì)對(duì)射頻電路芯片電路與版圖設(shè)計(jì)帶來(lái)新的技術(shù)挑戰(zhàn)和產(chǎn)品需求���。

因此, 在5G 和IoT時(shí)代, 無(wú)論是標(biāo)準(zhǔn)單元版圖設(shè)計(jì),半定制版圖設(shè)計(jì)和全定制版圖設(shè)計(jì),基本的設(shè)計(jì)方法得到發(fā)揚(yáng)傳承,高性能��、低功耗����、低成本的要求提得更高,對(duì)未來(lái)高質(zhì)量高可靠性版圖設(shè)計(jì)設(shè)立了新的規(guī)范和起點(diǎn)���。例如�,用于深度學(xué)習(xí)的芯片設(shè)計(jì),由于涉及到海量數(shù)據(jù)計(jì)算���,已經(jīng)使用算力單位千兆(1012, tera operations per second, TOPS)為參考,使用能效比(TOPS/W)作為衡量芯片架構(gòu)和設(shè)計(jì)的總體檢測(cè)指標(biāo)�����。最新的2019年國(guó)際固體電路會(huì)議(International Solid-State Circuits Conference, ISSCC)分組文章都做了詳盡的討論�����。

參考文獻(xiàn)

[1] 王陽(yáng)元主編,《集成電路產(chǎn)業(yè)全書(shū)》,2018年,北京:電子工業(yè)出版社(ISBN 978-7-121-34822-8)�。

[2] 陳春章,集成電路設(shè)計(jì)方法中EDA的角色��,《微納創(chuàng)新》���,2018年夏�����,總第08期��,第34~39頁(yè)��。

[3] 陳春章,王國(guó)雄,艾霞,《數(shù)字集成電路物理設(shè)計(jì)》,2008年,北京:科學(xué)出版社(ISBN 978-7-03-022031-8)��。

[4] ISSCC 2019,https://submissions.mirasmart.com/ISSCC2019/PDF/ISSCC2019AdvanceProgram.pdf