【導(dǎo)讀】隨著高級工藝的演進(jìn),電路設(shè)計團(tuán)隊在最先進(jìn)的晶片上系統(tǒng)內(nèi)加載更多功能和性能的能力日益增強。與此同時,他們同樣面臨許多新的設(shè)計挑戰(zhàn)。

多重圖案拆分給設(shè)計實施過程帶來了許多重大布局限制,另外為降低功耗和提高性能而引入 FinFET 晶體管使之更加復(fù)雜,因為它對擺設(shè)和布線流程帶來了更多的限制。適用于高級工藝設(shè)計的物理實現(xiàn)工具必須針對引入多重圖案拆分和 FinFET 后的擺設(shè)、布線、DFM、提取和時序進(jìn)行增強。

對布線的挑戰(zhàn)

包括多重圖案拆分規(guī)則在內(nèi)的設(shè)計規(guī)則的復(fù)雜性和數(shù)量已經(jīng)顯著提升,這對布線程序提出了巨大的挑戰(zhàn)。

FinFET 同樣帶來了更多限制,例如電壓閾值感知間隔、植入層規(guī)則等。這些因素將影響擺設(shè)、布局規(guī)劃和優(yōu)化引擎,還會直接影響設(shè)計的利用率和面積。多重圖案拆分收斂和時序收斂相互依存,可以增加設(shè)計收斂時間。

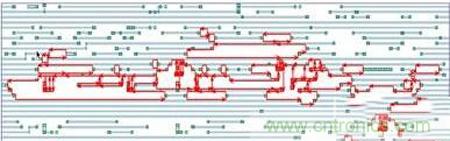

圖1:較長的全局奇回路違規(guī)

布線程序必須能夠自動理解顏色,檢測并修復(fù)多重圖案拆分違規(guī),還能夠?qū)ζ溥M(jìn)行驗證。傳統(tǒng)的 DRC 違規(guī)往往是局部的,多重圖案拆分違規(guī)與之不同,如圖1所示,它們在本質(zhì)上可能是全局性的,不僅會影響多個形狀,還會在奇回路修復(fù)過程中使計算變得極其密集和困難。對布局的任何干擾都有可能產(chǎn)生新的多重圖案拆分違規(guī),使信號完整性收斂和多重圖案拆分收斂變得極具挑戰(zhàn)性。

由于預(yù)先存在的形狀、電源和接地軌道可能導(dǎo)致較長的利用密集內(nèi)存進(jìn)行驗證的運行時間,因此需要特別考慮金屬1層的布線選擇。像非優(yōu)選慢移這樣的傳統(tǒng)技術(shù)不能用于解決可布線性問題,因為多重圖案拆分中禁止使用這些技術(shù)。多重圖案拆分利用軟規(guī)則來預(yù)防問題,這的確減少了出現(xiàn)多重圖案拆分奇回路的可能性,但是僅僅依賴預(yù)防會使設(shè)計變得非常被動。高效的多重圖案拆分收斂需要對布線程序架構(gòu)進(jìn)行更新,新架構(gòu)要有自己的本地色調(diào)、驗證和沖突解決引擎。

對擺放的挑戰(zhàn)

實現(xiàn)工具需要考慮流程的每個階段的雙重圖案拆分限制和 FinFET 布局限制之間的相互作用,包括擺放、布線和優(yōu)化。工具必須遵守大量位置和路徑布局規(guī)則,例如定位時標(biāo)準(zhǔn)單元和宏的鰭網(wǎng)格對齊規(guī)則、最小面積間隔規(guī)則以及源極-漏極對接規(guī)則。在擺放期間,全局布線程序必須考慮這些規(guī)則,同時計算雙圖案結(jié)構(gòu)層上的資源。通常情況下,這意味著這些層上部署的網(wǎng)數(shù)會更少,不像基本負(fù)載/容量計算中的那樣多。準(zhǔn)確對針腳密度建模的能力是非常重要的,因為各個單元需要隔開以便輕松實現(xiàn)線與針腳的連接。在擺放期間,實現(xiàn)工具還必須對擁塞進(jìn)行建模,提前對擁塞進(jìn)行估計必須很好地關(guān)聯(lián)詳細(xì)的布線結(jié)果。

對優(yōu)化的挑戰(zhàn)

通常,優(yōu)化高級工藝設(shè)計是為了在不影響面積大小的前提下獲得最佳的性能和功耗。由于存在嚴(yán)格的多重圖案拆分和 FinFET 規(guī)則和限制,設(shè)計利用率和面積日益成為設(shè)計團(tuán)隊眼中更大的挑戰(zhàn)。盡管 FinFET 大大降低了總功耗,但是由于寄生電阻和電容以及針腳電容均有所提高,動態(tài)功耗成分更高(與漏電相比)。多重圖案拆分和時序收斂解決方案之間存在沖突,信號完整性收斂因而變得更加困難。有時設(shè)計師可以結(jié)束兩者之間的“乒乓效應(yīng)”,但這意味著每個已有違規(guī)上又出現(xiàn)了新的違規(guī)。為了避免這種問題,工具就需要使用新的技術(shù),因為布線擴(kuò)展和非優(yōu)先慢移等老技術(shù)已經(jīng)不再有效。優(yōu)化引擎必須自動了解多重圖案拆分和 FinFET 規(guī)則,以便同時解決功耗、性能和面積上的要求。

結(jié)論

由于多重圖案拆分的引入、FinFET 設(shè)備、復(fù)雜的 DRC/DFM 要求,更多的設(shè)計尺寸和多個設(shè)計目標(biāo)等等因素,使高級工藝設(shè)計面臨一系列重大設(shè)計挑戰(zhàn)。