【導讀】電阻串 DAC 有時被稱為 Kelvin 分壓器或 Kelvin-Varley 分壓器(以其發(fā)明者命名),是用于 DAC 設計最直接的方法之一。最簡單的電阻串 DAC 只是一系列相同尺寸的電阻器和每個電阻器之間的接點。

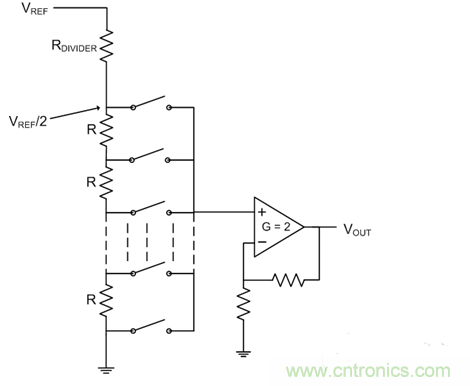

電阻串 DAC 有時被稱為 Kelvin 分壓器或 Kelvin-Varley 分壓器(以其發(fā)明者命名),是用于 DAC 設計最直接的方法之一。最簡單的電阻串 DAC 只是一系列相同尺寸的電阻器和每個電阻器之間的接點。適當的接點可根據應用于 DAC 的數字代碼切換至輸出緩沖器。這種有限開關活動可產生極低的干擾能量。在理想情況下,每個電阻器都會針對等于 1 LSB 的參考電壓產生壓降。下圖是該架構的簡單說明。

隨著電阻串 DAC 中分辨率的提高,設計所需的電阻器數量也在呈指數級增長。一個 n 位電阻串 DAC 需要 2n 個電阻器,因此高分辨率電阻串 DAC 通常需要大型 IC 封裝。這就意味著 16 位 DAC 需要 65,536 個電阻器,18 位需要 262,144 個,而 20 位則需要 1,048,576 個電阻器!級聯分段技術有時可用來減少所需的電阻器數量,但對于我們的用途而言,我們將不考慮分段技術,因為即使實施了分段,架構趨勢在應用層面也更傾向于實用。

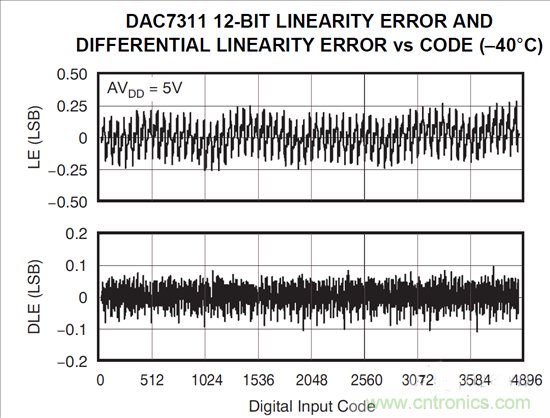

每個電阻器值的精確度可直接決定線性度。如果電阻串中任何一個電阻器的值不合適,我們就會在代碼轉換時發(fā)現相對于該電阻器的不良微分非線性度 (DNL)。此外,所有后續(xù)代碼的積分非線性度 (INL) 也會因為不匹配而產生失調。由于典型電阻串 DAC 設計中的電阻器數量龐大,我們不可能對每個電阻器都進行調整,因此只能接受一定程度上的 DNL 誤差。然而,仍然必須維持良好的 INL 性能,因此可經常對各組電阻器實施區(qū)域化調整,以避免調整每個電阻器,其在以下 INL 圖中呈“階梯”狀。

電阻串 DAC 的一個額外優(yōu)勢是:從參考輸入看,除了在瞬間代碼轉換階段外,輸入阻抗都可保持恒定。其它數據轉換器架構(尤其是 SAR ADC)具有動態(tài)加載條件,需要一個參考緩沖器,而電阻串 DAC 就沒這個必要。然而一般來說,應該對任何參考進行緩沖,尤其是在輸入/輸出隨高頻率變化時。還需要重點關注的是參考等效輸入阻抗通常都非常高,可使大多數電阻串 DAC 具有極高的電源效率。

電阻串 DAC 設計最終、最微妙的元件是位于串電阻器及接點之前的分壓器。該電阻器電阻等于串中其余電阻器的等效阻抗,能有效將參考輸入減半。這樣做的目的是降低輸出緩沖器的共模輸入要求,并在實現良好性能的同時幫助保持低成本。為了對此進行補償,輸出緩沖器一般采取 2 倍的非反相增益,盡管有時反饋電阻器通過數字控制實現不同增益。

電阻串 DAC 需要記住的幾個特性:

·簡化設計,實現低成本;

·低干擾能量;

·固有的單調性;

·低功耗。

電阻串 DAC 通??稍诒銛y式電池供電應用中找到用武之地,充分發(fā)揮其低功耗優(yōu)勢。此外,電阻串 DAC 還適用于可充分利用其固有單調特性的閉環(huán)控制系統等應用,以及各種低成本應用,在該應用中 DAC 只為系統提供一些校準特性,而不會像我們在其它 DAC 應用中可能看到的那樣,擔任“主角”。