【導(dǎo)讀】通常認(rèn)為�,平均電流模式控制的性能可充分滿(mǎn)足大部分 50/60Hz AC 線(xiàn)路輸入的商用電源應(yīng)用需求。但是���,傳統(tǒng)平均電流模式控制會(huì)使電感器電流領(lǐng)先于輸入電壓��,導(dǎo)致不統(tǒng)一的基本位移功率因數(shù)與過(guò)零失真���。在 PFC 工作在高頻率 AC 環(huán)境下時(shí)�����,這種情況會(huì)變得更糟糕�,例如工作在 400Hz 下的機(jī)載系統(tǒng)。這些系統(tǒng)所需的高質(zhì)量輸入電流很難通過(guò)傳統(tǒng)控制方法實(shí)現(xiàn)�。一種名為占空比前饋 (DFF) 控制的最新控制方法可有效降低高線(xiàn)路頻率下的輸入電流失真1/2/3。

幾十年來(lái)�����,平均電流模式控制一直用于功率因數(shù)校正 (PFC)���,而且在商業(yè)市場(chǎng)也有各種采用這種控制算法的 PFC 控制芯片�。

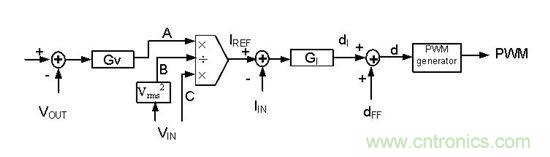

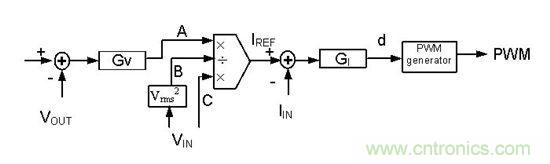

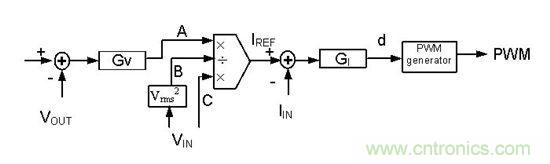

圖 1 是這種平均電流模式控制的形象介紹���。

圖 1. PFC 的平均電流模式控制

通常認(rèn)為�����,平均電流模式控制的性能可充分滿(mǎn)足大部分 50/60Hz AC 線(xiàn)路輸入的商用電源應(yīng)用需求�����。但是�,傳統(tǒng)平均電流模式控制會(huì)使電感器電流領(lǐng)先于輸入電壓�,導(dǎo)致不統(tǒng)一的基本位移功率因數(shù)與過(guò)零失真���。在 PFC 工作在高頻率 AC 環(huán)境下時(shí),這種情況會(huì)變得更糟糕�����,例如工作在 400Hz 下的機(jī)載系統(tǒng)�����。這些系統(tǒng)所需的高質(zhì)量輸入電流很難通過(guò)傳統(tǒng)控制方法實(shí)現(xiàn)�����。一種名為占空比前饋 (DFF) 控制的最新控制方法可有效降低高線(xiàn)路頻率下的輸入電流失真1/2/3���。

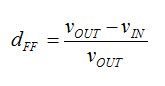

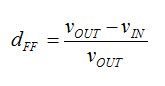

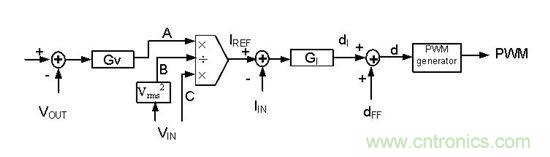

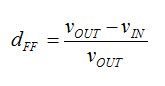

DFF 控制的基本構(gòu)想是預(yù)先計(jì)算占空比,以減輕反饋控制器的任務(wù)�。對(duì)于工作在連續(xù)傳導(dǎo)模式下的升壓拓?fù)鋪?lái)說(shuō),占空比 dFF 的計(jì)算公式為:

公式 1

該占空比模式在開(kāi)關(guān)兩端產(chǎn)成一個(gè)電壓�,其在整個(gè)開(kāi)關(guān)周期內(nèi)的平均值等于整流輸入電壓。常規(guī)電流環(huán)路補(bǔ)償器會(huì)圍繞這個(gè)計(jì)算出的占空比模式改變占空比��。

由于升壓電感器在線(xiàn)路頻率下的阻抗非常低����,因此很小的占空比變化就會(huì)在整個(gè)電感器上產(chǎn)生足夠的電壓�,以生成所需的正弦電流波形��。

圖 2. PFC 的占空比前饋控制

圖 2 是獲得的控制方案�����。公式 1 可計(jì)算前饋占空比 dFF����。然后它可添加至傳統(tǒng)平均電流模式控制輸出 dI。最終的占空比 d 可用來(lái)生成控制 PFC 的脈寬調(diào)制 (PWM) 波形�����。

使用 DFF 控制時(shí)����,需要很多數(shù)學(xué)計(jì)算�����。CPU 的速度可決定控制環(huán)路的速度,進(jìn)而影響環(huán)路帶寬���。更快的 CPU 就意味著可實(shí)現(xiàn)更高的帶寬���。然而,這也意味著更高的成本與功耗��。

當(dāng)我使用德州儀器 (TI) 數(shù)字控制器 UCD3138 實(shí)施這一控制算法時(shí)��,我利用 UCD3138 的硬件數(shù)字補(bǔ)償器以相對(duì)較低的 CPU 速度實(shí)現(xiàn)了高帶寬����。

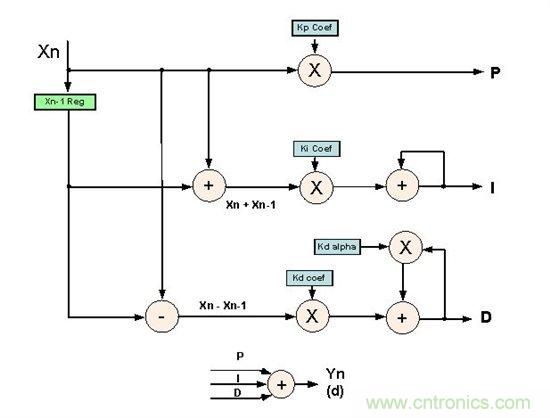

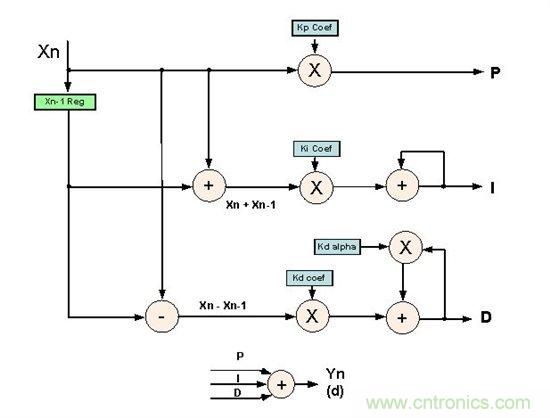

UCD3138 中的數(shù)字補(bǔ)償器是一個(gè)增加了一個(gè) α 的傳統(tǒng) PID 結(jié)構(gòu),可提供雙極雙零補(bǔ)償(圖 3)�。P�、I 和 D 是三個(gè)獨(dú)立分支,合并輸出后可生成最終的控制信號(hào)��。數(shù)字補(bǔ)償器運(yùn)行速率高達(dá) 2MHz���。由于 PFC 電流環(huán)路是一階系統(tǒng)�����,因此通常情況下 PI 控制器已足夠進(jìn)行補(bǔ)償����。這可騰出 D 分支,用來(lái)提高 DFF 控制速度��。

仔細(xì)觀(guān)察圖 2�。盡管 IREF 和 dFF 由速度有限的 CPU 計(jì)算,但數(shù)字補(bǔ)償器和 PWM 生成器是 UCD3138 的硬件���,因此它們的運(yùn)行速度更快��。這就意味著 dI 能以高速進(jìn)行計(jì)算����。因而其實(shí) dFF + dI = d����,其可降低控制環(huán)路速度。如果 dFF + dI = d 也能通過(guò)硬件完成���,那么不僅整個(gè)環(huán)路速度會(huì)比以前快�����,而且?guī)捯矔?huì)提高���。

圖 3. UCD3138 的 PID 結(jié)構(gòu)

D 分支有兩個(gè)高級(jí)特性:

1. 輸出可設(shè)置為預(yù)定義值

2. 它可能會(huì)中止(凍結(jié))�����,使其輸出維持當(dāng)前值

我們可利用這兩個(gè)特性增強(qiáng) DFF 控制�����。

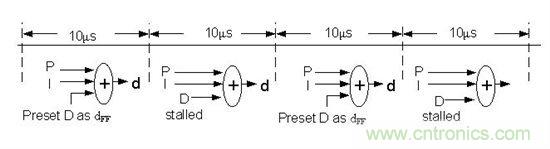

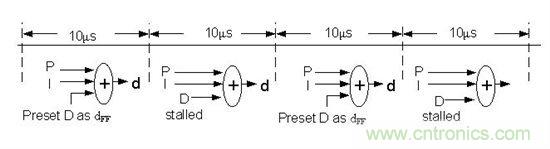

例如�����,電流控制環(huán)路必須是 100KHz��,但由于 CPU 速度的限制����,dFF 最多只能在 50KHz 速率下進(jìn)行計(jì)算���。完成計(jì)算后,將 D 分支輸出預(yù)設(shè)為 dFF�,然后中止。盡管 dFF 在 50kHz 下計(jì)算,但是 P�����、I 和 d = P + I + dFF 都在更快的 100KHz 速率下運(yùn)行���,因此 PWM 可在 100kHz 下更新�����。有效的控制環(huán)路將在 100kHz 下運(yùn)行��。該過(guò)程請(qǐng)參見(jiàn)圖 4��。

圖 4. 將 DFF 與 UCD3138 PID 結(jié)構(gòu)結(jié)合

有了更快的控制環(huán)路速度�����,就可提高帶寬�,從而改善 THD 和 PF����。UCD3138 的獨(dú)特結(jié)構(gòu)可提供改進(jìn)的 DFF 實(shí)施方案。

推薦閱讀:

公式 1

公式 1

公式 1

公式 1