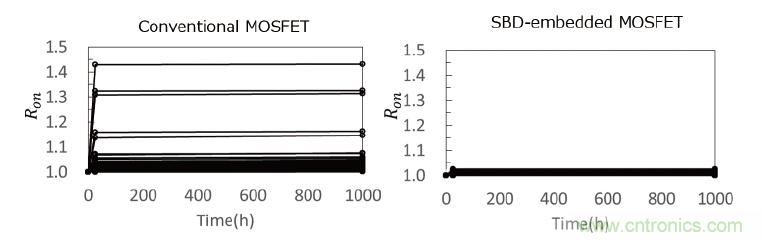

【導讀】東京——東芝電子元件及存儲裝置株式會社(簡稱“東芝”)今日宣布了一種可提高碳化硅(SiC)MOSFET[1]可靠性的新器件結構問世。相較于東芝的典型器件結構,MOSFET內(nèi)嵌的肖特基勢壘二極管[2](SBD)可在抑制導通電阻增大的同時,將器件結構的可靠性提高10倍以上[3]。

功率器件是降低車輛以及工業(yè)設備和其它電氣設備能耗的重要元器件,而碳化硅相較于有機硅可進一步提高電壓并降低損耗,因此業(yè)界普遍預期碳化硅將成為新一代的功率器件材料。雖然碳化硅材質的功率器件目前主要用于列車逆變器,但其今后的應用領域非常廣泛,包括用于工業(yè)設備的各種光伏發(fā)電系統(tǒng)(PPS)和電源管理系統(tǒng)(PMS)。

目前可靠性問題是碳化硅器件利用和市場增長的攔路虎,問題之一涉及位于功率MOSFET的電源與列車之間的PN結二極管[4]。PN結二極管的外施電壓使其帶電,造成導通電阻變化,進而有損于器件的可靠性。東芝新推出的肖特基勢壘二極管(SBD)內(nèi)嵌式MOSFET器件結構正是此問題的克星。

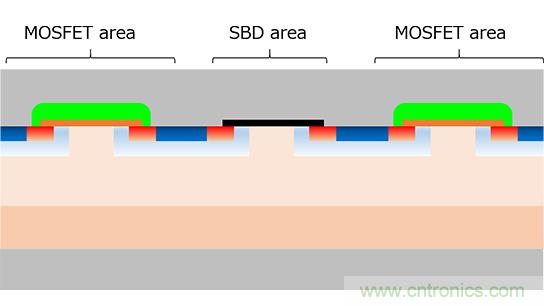

該新結構中有一個與電池單元內(nèi)的PN結二極管平行設置的肖特基勢壘二極管,可防止PN結二極管帶電。相較于PN結二極管,內(nèi)嵌肖特基勢壘二極管的通態(tài)電壓更低,因此電流會通過內(nèi)嵌肖特基勢壘二極管,進而抑制導通電阻變化和MOSFET可靠性下降等問題。

內(nèi)嵌肖特基勢壘二極管的MOSFET現(xiàn)已投入實際應用,但僅限于3.3kV器件等高壓產(chǎn)品;內(nèi)嵌肖特基勢壘二極管通常會使導通電阻升高至僅高壓產(chǎn)品能承受的一個電壓水平。東芝在調整各個器件參數(shù)后發(fā)現(xiàn)MOSFET中肖特基勢壘二極管的面積比是抑制導通電阻增大的關鍵因素。東芝通過優(yōu)化肖特基勢壘二極管的這一比例,實現(xiàn)了1.2kV級高可靠型碳化硅(SiC)MOSFET。

東芝計劃自今年八月下旬起利用這項新技術開始量產(chǎn)1.2kV級碳化硅(SiC)MOSFET。

2020年7月德國紐倫堡國際電力電子系統(tǒng)及元器件展覽會(PCIM Europe)上報道了該新器件結構的詳情,這是一次在線舉辦的國際性功率半導體展會。

注

[1] MOSFET:金屬氧化物半導體場效應晶體管

[2] 肖特基勢壘二極管(SBD):通過半導體與金屬接合形成的一種半導體二極管

[3] 東芝規(guī)定當以250A/cm2的電流密度通過電源向某器件的漏極通電1,000小時后才出現(xiàn)導通電阻變化,即視為該器件可靠。東芝的典型MOSFET的導通電阻變化率高達43%,而肖特基勢壘二極管(SBD)內(nèi)嵌式MOSFET的這一變化率僅為3%。

[4] PN結二極管:通過在電源與漏極之間設置PN結形成的一種二極管

肖特基勢壘二極管(SBD)內(nèi)嵌式MOSFET的結構

肖特基勢壘二極管(SBD)內(nèi)嵌式MOSFET可抑制導通電阻變化

推薦閱讀: