【導(dǎo)讀】隨著射頻集成電路(RFIC)中集成的元件不斷增多,噪聲耦合源也日益增多,使電源管理變得越來越重要。本文將描述電源噪聲可能對RFIC 性能造成的影響。雖然本文的例子是集成鎖相環(huán)(PLL)和電壓控制振蕩器(VCO)的 ADRF6820 正交解調(diào)器,但所得結(jié)果也適用于其他高性能RFIC。

電源噪聲會在解調(diào)器中形成混頻積,因而可能導(dǎo)致線性度下降,并對PLL/VCO 中的相位噪聲性能造成不利影響。本文將詳細(xì)描述電源評估方案,同時(shí)提供采用低壓差調(diào)節(jié)器(LDO)和開關(guān)調(diào)節(jié)器的推薦電源設(shè)計(jì)。

憑借雙電源和超高RF 集成度,ADRF6820 是適合討論的一款理想器件。它使用的有源混頻內(nèi)核與 ADL5380 正交解調(diào)器相似,PLL/VCO 內(nèi)核與 ADRF6720 相同,因此,本文所提供信息也可用于這些器件。另外,電源設(shè)計(jì)也可用于要求3.3 V 或5.0 V電源、功耗相似的新型設(shè)計(jì)。

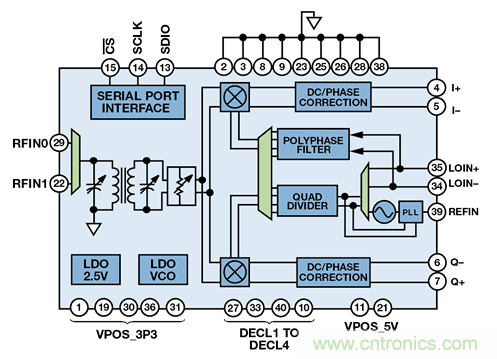

ADRF6820 正交解調(diào)器和頻率合成器(如圖1 所示)非常適合新一代通信系統(tǒng)。該器件功能豐富,包括一個(gè)高線性度寬帶I/Q 解調(diào)器、一個(gè)集成小數(shù)N 分頻PLL 和一個(gè)低相位噪聲多核VCO。另外集成一個(gè)2:1 RF 開關(guān)、一個(gè)可調(diào)諧RF 巴倫、一個(gè)可編程RF衰減器和兩個(gè)LDO。這款高度集成的RFIC 采用6 mm × 6 mmLFCSP 封裝。

圖1. ADRF6820 簡化功能框圖

電源靈敏度

受電源噪聲影響最大的模塊為混頻器內(nèi)核和頻率合成器。耦合至混頻器內(nèi)核的噪聲會形成無用信號,結(jié)果會導(dǎo)致線性度和動態(tài)范圍下降。這對正交解調(diào)器尤其重要,因?yàn)榈皖l混頻積在目標(biāo)頻帶之內(nèi)。類似地,電源噪聲可能導(dǎo)致PLL/VCO 相位噪聲性能下降。無用混頻產(chǎn)物和相位噪聲性能下降是多數(shù)混頻器和頻率合成器的常見問題,但確切的下降幅度取決于芯片的架構(gòu)和布局。了解這些電源靈敏度有利于設(shè)計(jì)出更加魯棒的電源,使性能和效率達(dá)到最優(yōu)。

正交解調(diào)器靈敏度

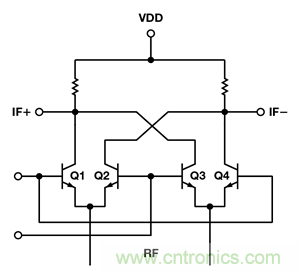

ADRF6820 采用一個(gè)雙平衡吉爾伯特單元有源混頻器內(nèi)核,如圖2 所示。雙平衡意味著LO 和RF 端口都采用差分驅(qū)動方式。

圖2. 吉爾伯特單元雙平衡有源混頻器

在濾波器抑制高階諧波以后,所得到的混頻器輸出為RF 和LO輸入的和與差。差項(xiàng)(也稱為IF 頻率)在目標(biāo)頻帶之內(nèi),是所需信號。和項(xiàng)在頻帶之外,要進(jìn)行濾波處理。

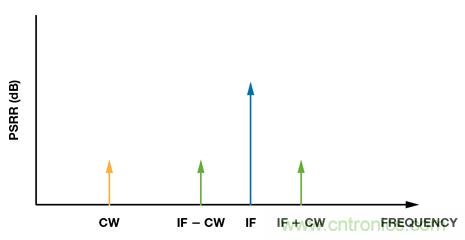

理想情況下,只有所需RF 和LO 信號會輸入混頻器內(nèi)核,但很少是這種情況。電源噪聲可能耦合到混頻器輸入中并表現(xiàn)為混頻雜散。根據(jù)噪聲耦合源的不同,混頻雜散的相對幅度可能不同。圖3 所示為一種示例混頻器輸出頻譜,其中,由于電源噪聲的耦合,其與有用信號的混頻產(chǎn)物也出現(xiàn)在輸出頻譜上。在圖中,CW 對應(yīng)于耦合到供電線路的連續(xù)波或正弦信號。比如,噪聲可能是來自600 kHz 或1.2 MHz 開關(guān)調(diào)節(jié)器的時(shí)鐘噪聲。電源噪聲可能導(dǎo)致兩個(gè)不同的問題;如果噪聲耦合到混頻器輸出,CW 音將沒有經(jīng)過任何頻率轉(zhuǎn)換,出現(xiàn)在輸出端。如果耦合發(fā)生在混頻器輸入端,則CW 音會調(diào)制RF 和LO 信號,并在IF ± CW 產(chǎn)生積。

圖3. 電源噪聲耦合條件下的示例混頻器輸出頻譜

這些混頻積可能接近目標(biāo)IF 信號,因此,要濾除它們是很困難的,動態(tài)范圍損失是不可避免的。正交解調(diào)器尤其如此,因?yàn)樗鼈兊幕鶐菑?fù)數(shù)且以直流為中心。ADRF6820 的解調(diào)帶寬范圍為直流至600 MHz。如果用噪聲頻率為1.2 MHz 的開關(guān)調(diào)節(jié)器驅(qū)動混頻器內(nèi)核,則無用混頻積會出現(xiàn)在IF ± 1.2 MHz。

頻率合成器靈敏度

本文末尾的參考文獻(xiàn)針對電源噪聲如何影響集成PLL和VCO提供了非常有價(jià)值的信息。其原理適用于采用相同架構(gòu)的其他設(shè)計(jì),但不同的設(shè)計(jì)需要單獨(dú)進(jìn)行電源評估。例如,ADRF6820VCO 電源上的集成LDO 比不采用集成LDO 的PLL 電源具有更強(qiáng)的噪聲抑制能力。

ADRF6820 電源域和功耗

ADRF6820 電源域和功耗

ADRF6820 的每個(gè)主要功能模塊都有自己的電源引腳。兩個(gè)域由5 V 電源供電。VPMX 驅(qū)動混頻器內(nèi)核,VPRF 驅(qū)動RF 前端和輸入開關(guān)。其他域由3.3 V 電源供電。VPOS_DIG 驅(qū)動一個(gè)集成LDO,后者輸出2.5 V 以驅(qū)動SPI 接口、PLL 的Σ-Δ 調(diào)制器和頻率合成器的FRAC/INT 分壓器。VPOS_PLL 驅(qū)動PLL 電路,包括參考輸入頻率(REFIN)、相位頻率檢測器(PFD)和電荷泵(CP)。VPOS_LO1 和VPOS_LO2 驅(qū)動LO 路徑,包括基帶放大器和直流偏置基準(zhǔn)電壓源。VPOS_VCO 驅(qū)動另一個(gè)集成LDO,后者輸出2.8 V 以驅(qū)動多核VCO。該LDO 對降低對電源噪聲的靈敏度十分重要。

ADRF6820 可配置為多種工作模式。正常工作模式下,采用2850 MHz LO 時(shí),功耗小于1.5 mW。降低偏置電流會同時(shí)降低功耗和性能。增加混頻器偏置電流會提高混頻器內(nèi)核的線性度并改善IIP3,但會降低噪聲系數(shù),增加功耗。如果噪聲系數(shù)非常重要,可以降低混頻器偏置電流,結(jié)果可減少混頻器內(nèi)核中的噪聲并降低功耗。類似地,輸出端的基帶放大器對低阻抗輸出負(fù)載具有可變電流驅(qū)動能力。低輸出阻抗負(fù)載要求較高的電流驅(qū)動,功耗也更高。數(shù)據(jù)手冊列出了一些數(shù)據(jù)表,其中展示了各種工作模式下的功耗。

測量步驟和結(jié)果

供電軌上的噪聲耦合會在CW 和IF ± CW 時(shí)產(chǎn)生無用噪聲。要模擬該噪聲耦合情形,在每個(gè)電源引腳上施加一個(gè)CW 音,測量所形成的混頻積相對于輸入CW 音的幅度。把該測量值記為電源抑制能力,單位為dB。電源抑制因頻率而異,因此,要對30 kHz 至1 GHz 的CW 頻率進(jìn)行掃描,以捕捉到具體的行為數(shù)據(jù)。目標(biāo)頻帶內(nèi)的電源抑制能力決定了是否需要濾波。PSRR 計(jì)算方法如下:

CW PSRR in dB = input CW amplitude (dBm) – measured CW feedthrough at I/Q output (dBm)

(IF ± CW) PSRR in dB = input CW amplitude (dBm) – measured IF ± CW feedthrough at I/Q output (dBm)

(IF + CW) in dBm = (IF – CW) dBm, as CW tones modulated around the carrier have equal amplitudes

實(shí)驗(yàn)室設(shè)置

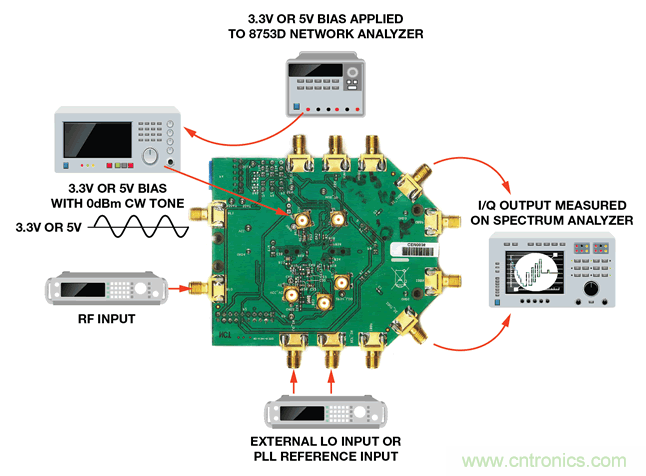

圖4 所示為實(shí)驗(yàn)室設(shè)置。向網(wǎng)絡(luò)分析儀施加一個(gè)3.3 V 或5 V 直流源,以產(chǎn)生失調(diào)為3.3 V 或5 V 的掃頻連續(xù)正弦信號。將該信號施加到RFIC 上的各個(gè)供電軌。兩個(gè)信號發(fā)生器提供RF 和LO輸入信號。測量頻譜分析儀的輸出。

圖4. ADRF6820 PSRR 測量設(shè)置

測量步驟

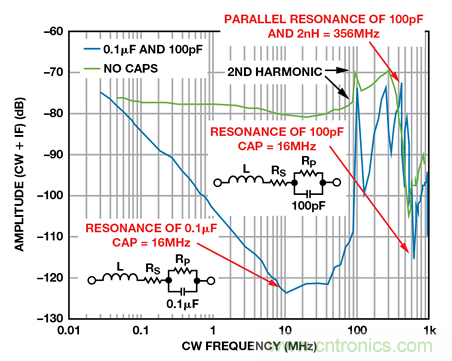

無用混頻積的幅度取決于芯片的電源抑制性能,以及評估板上去耦電容的大小和位置。圖5 所示為輸出端(IF + CW)音的幅度,其中,電源引腳上給定0 dB 的正弦信號。無去耦電容時(shí),無用音的幅度在–70 dBc 和–80 dBc 之間。數(shù)據(jù)手冊建議在板正面器件旁邊設(shè)置一個(gè)100 pF 的電容,在背面設(shè)置一個(gè)0.1 μF 的電容。從圖中可以看到這些外部去耦電容的諧振。16 MHz 處的瞬變是0.1 μF 電容諧振的結(jié)果(寄生電感為1 nH)。356 MHz 處的瞬變是100 pF 電容諧振的結(jié)果(兩個(gè)電容的寄生電感均為2 nH)。500 MHz 處的瞬變是100 pF 電容諧振的結(jié)果(寄生電感為1nH)。

圖5. IF ± CW去耦電容諧振的影響

結(jié)果

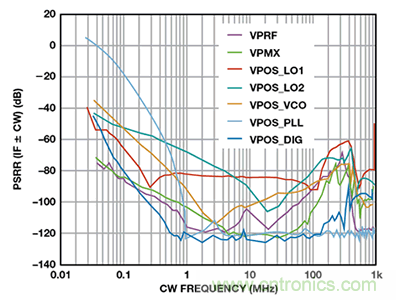

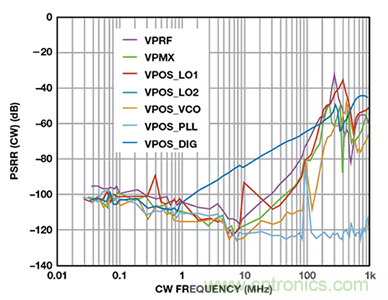

測量了基帶輸出端的供電軌上干擾信號(CW)和調(diào)制信號(IF ± CW)的幅度。在被測供電軌上引入了噪聲,其他電源則保持潔凈。圖6 所示為在電源引腳上注入0 dB 正弦信號并在30 kHz 至1 GHz 范圍內(nèi)掃頻時(shí)(IF ± CW)音的幅度。圖7 所示為從CW 音到基帶輸出的饋通。

圖6. (IF ± CW)音的PSRR

圖7. CW音的PSRR

分析

圖中提供了各電源引腳處的電源靈敏度數(shù)據(jù),這些數(shù)據(jù)非常有用。VPOS_PLL 具有最差電源抑制性能,因此,是最靈敏的電源節(jié)點(diǎn)。該電源引腳驅(qū)動PLL 電路,包括參考輸入頻率、相位頻率檢測器和電荷泵。這些靈敏的功能模塊決定著LO 信號的精度和相位性能,因此,其上耦合的任何噪聲都會直接傳播到輸出端。

同理,可以認(rèn)為VCO 電源也是一個(gè)非常重要的節(jié)點(diǎn)。從圖中可以看出,VPOS_VCO 的抑制性能遠(yuǎn)遠(yuǎn)優(yōu)于VPOS_PLL。這是實(shí)際驅(qū)動VCO 的內(nèi)置LDO 造成的結(jié)果。LDO 將VCO 與外部引腳上的噪聲隔離開,同時(shí)為其提供固定噪聲頻譜密度。PLL 電源無LDO,因而是最敏感的供電軌??梢?,將其與潛在噪聲耦合相隔離對于獲得最佳性能至關(guān)重要。

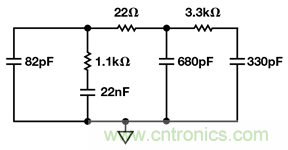

PLL 環(huán)路濾波器會衰減高CW 頻率,因此,VPOS_PLL 在低頻下的靈敏度較差,當(dāng)頻率從30 kHz 掃描至1 GHz 時(shí)會緩慢改善。在較高頻率下,干擾音的幅度會衰減,注入PLL 的功率水平顯著降低??梢?,VPOS_PLL 的高頻電源抑制性能優(yōu)于其他電源域。環(huán)路濾波器組件是針對20 kHz 配置的,如圖8 所示。

供電軌(從靈敏度最高到最低)為:VPOS_PLL、VPOS_LO2、VPOS_VCO、VPOS_LO1、VPOS_DIG、VPMX 和VPRF。

圖8. 針對20 kHz 環(huán)路帶寬配置的PLL 環(huán)路濾波器

電源設(shè)計(jì)

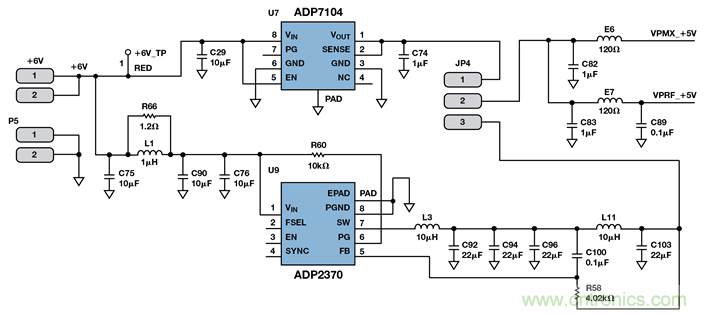

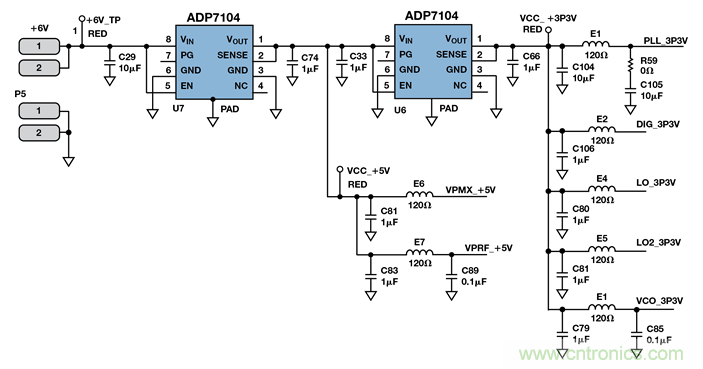

經(jīng)過前面的討論,我們對ADRF6820 在各種模式下的最大功耗以及各電源域的靈敏度有了較好的理解,我們利用開關(guān)調(diào)節(jié)器和LDO 來設(shè)計(jì)電源管理解決方案,以決定兩種電源解決方案的可行性。首先,把一個(gè)6 V 源調(diào)節(jié)至5 V 和3.3 V,供ADRF6820供電軌使用。圖9 所示為針對VPMX 和VPRF 的5 V 電源設(shè)計(jì)。ADP7104 CMOS LDO 最多可以提供500 mA 的負(fù)載電流。ADP2370 低靜態(tài)電流降壓開關(guān)調(diào)節(jié)器可以在1.2 MHz 或600 kHz 下工作。在開關(guān)調(diào)節(jié)器輸出端增加了額外的濾波理,以衰減開關(guān)噪聲。ADP2370 最高可以提供800 mA 的負(fù)載電流。ADRF6820 的5 V 供電軌可以由ADP7104 或ADP2370 驅(qū)動。在每個(gè)電源引腳上施加額外的去耦和濾波處理。

圖9. 5 V 電源設(shè)計(jì)

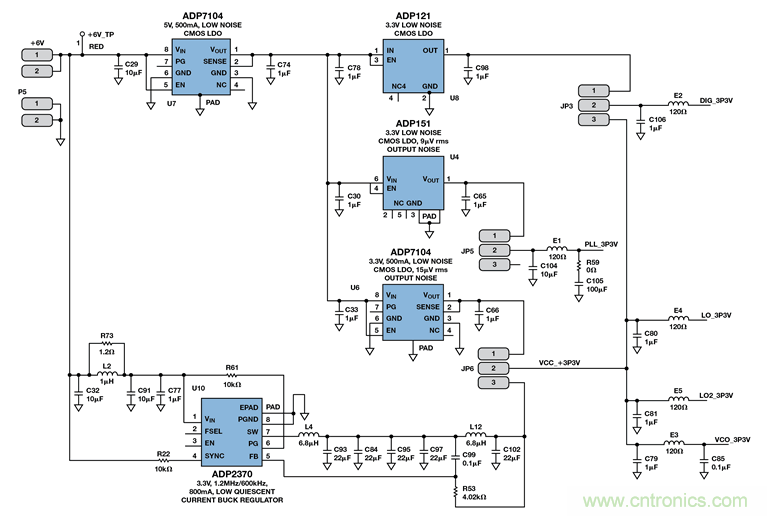

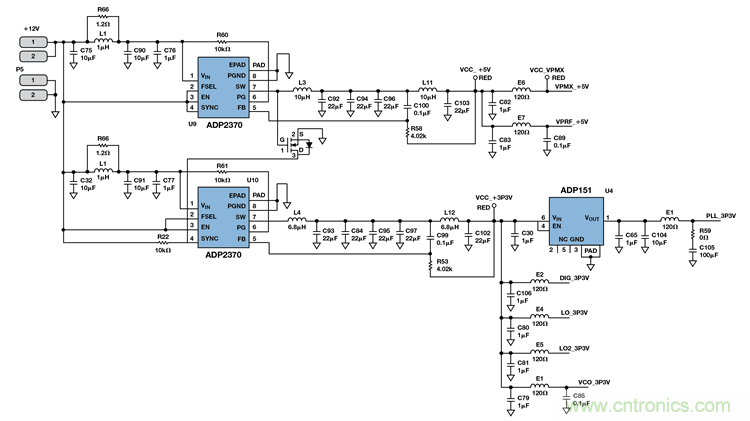

圖10 所示為3.3 V 電源設(shè)計(jì)。源電壓仍為6.0 V,但一個(gè)額外的LDO 使源電壓降至中間電壓,然后,源電壓進(jìn)一步降至3.3 V。需要一個(gè)額外級以減少功率損耗,因?yàn)橐粋€(gè)直接降壓至3.3 V 的6 V 源電壓工作時(shí)的最大效率為55%。開關(guān)調(diào)節(jié)器路徑不需要中間級,因?yàn)槠涿}沖寬度調(diào)制(PWM)架構(gòu)可降低功率損耗。

3.3 V 設(shè)計(jì)允許進(jìn)行更多實(shí)驗(yàn)。除了用一個(gè)LDO 或開關(guān)調(diào)節(jié)器驅(qū)動3.3 V 供電軌以外,VPOS_PLL 供電軌有額外LDO 選項(xiàng),VPOS_DIG 供電軌有一個(gè)可選的隔離式LDO。由于PLL 電源靈敏度最高,因此,我們嘗試了三種電源解決方案,每一種都有不同的輸出噪聲:ADP151 3.3 V 超低噪聲CMOS LDO,輸出噪聲為9 μV;ADP7104 3.3 V 低噪聲CMOS LDO,輸出噪聲為15 μV rms;ADP2370 3.3 V 降壓調(diào)節(jié)器。我們希望確定仍能維持所需相位噪聲性能的最高電源噪聲。最高性能、最低噪聲LDO是不可或缺的嗎?

另外還嘗試在VPOS_DIG 供電軌上采用 ADP121 3.3 V 低噪聲CMOS LDO,以確定數(shù)字噪聲是否會影響性能。受SPI 接口開關(guān)影響,數(shù)字供電軌的噪聲一般高于模擬電源。我們希望確定3.3 V 數(shù)字電源是需要自己的LDO,還是可以直接耦合到模擬電源。我們選擇ADP121 作為低成本解決方案。

圖10. 3.3 V 電源設(shè)計(jì)

結(jié)論和推薦電源設(shè)計(jì)

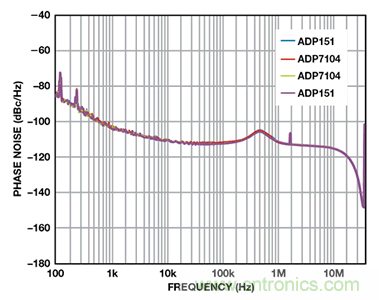

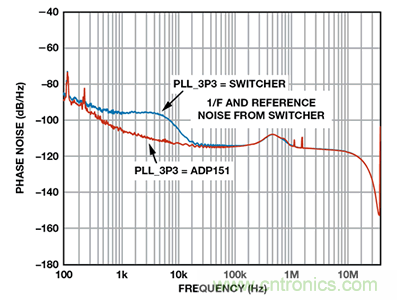

對于VPOS_PLL(最靈敏的供電軌),低成本的ADP151 LDO可以實(shí)現(xiàn)與ADP7104 高性能、低噪聲LDO 相同的相位噪聲,如圖11 所示。然而,在采用ADP2370 開關(guān)調(diào)節(jié)器時(shí),性能下降,如圖12 所示。噪聲波峰由開關(guān)調(diào)節(jié)器導(dǎo)致,在其輸出端可見,如圖13 所示。因此,VPOS_PLL 最多可以承受15 μV rms的噪聲而不造成集成相位噪聲性能下降,但不能使用開關(guān)調(diào)節(jié)器來驅(qū)動該引腳。使用性能更高、噪聲更低的LDO 并未帶來好處。

圖11. 使用ADP151 和ADP7104 時(shí)的集成相位噪聲

圖12. 使用ADP151 和ADP2370 時(shí)的集成相位噪聲

在用開關(guān)調(diào)節(jié)器或LDO 驅(qū)動剩余供電軌時(shí),可維持良好的相位噪聲性能,如圖14 所示。5 V 供電軌引腳VMPX 和VPRF 可以相連并用單電源供電。3.3 V 電源引腳VPOS_LO1、VPOS_LO2和VPOS_VCO 也可相連并用單電源供電。VPOS_DIG 不需要獨(dú)立的LDO,可以連接模擬3.3 V 電源。

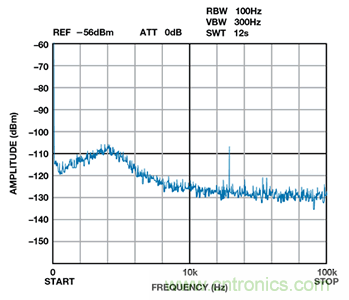

圖13. ADP2370 的輸出頻譜

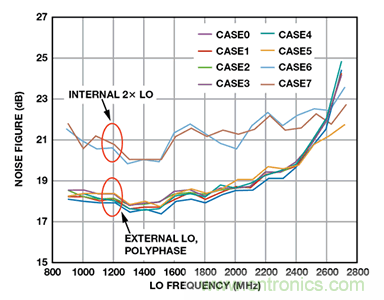

圖14. 開關(guān)與LDO 噪聲系數(shù)

推薦電源設(shè)計(jì)(如圖15 所示)采用6 V 源電壓,包括ADP7104 5.0 V 和ADP7104 3.3 V LDO。該解決方案只使用了LDO,因?yàn)樵措妷航咏璧碾娫措妷?。功效處于可接受水平,因此,無需額外增添濾波元件和開關(guān)調(diào)節(jié)器。

推薦的電源設(shè)計(jì)(如圖16 所示)采用12 V 源電壓,包括兩個(gè)開關(guān)調(diào)節(jié)器和一個(gè)LDO。源電壓遠(yuǎn)遠(yuǎn)大于所需電源電壓,因此使用了開關(guān)調(diào)節(jié)器來提高功效。除靈敏的VPOS_PLL 電源以外的所有電源引腳都可用開關(guān)調(diào)節(jié)器供電。ADP7104 或ADP151均可用于VPOS_PLL。

圖15. 6 V 源電壓的推薦電源設(shè)計(jì)

圖16. 12 V 源電壓的推薦電源設(shè)計(jì)

參考電路

電路筆記CN0147,利用低噪聲LDO 調(diào)節(jié)器為小數(shù)N 分頻壓控振蕩器(VCO)供電,以降低相位噪聲, ADI 公司,2010 年。

Collins, Ian. 集成PLL 和VCO[第2 部分]. Radio-Electronics.com,2010 年11 月。

調(diào)制器/解調(diào)器

線性穩(wěn)壓器

開關(guān)穩(wěn)壓器

推薦閱讀: